- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

AD封装库的元器件的边界是由topoverlayer决定的吗?

很是奇怪。一个器件的边界由silkscreen来决定,想加点标志都不行,会导致器件变大,layout的时候clearance通不过。

是AD太愚蠢,还是我没有搞对?

望指点。

你说的应该是不同器件之间的丝印间距报警吧...你可以将Silk To Silk Clearance间距关闭...不过布局的时候要自己心里有谱....想加标志在旁边空余处加就不会报错了...呵呵...我从来不开这个间距规则的...

哦?那如何控制几个器件的间距?

ad的component没有outline这一层,如何做?

哦?那如何控制几个器件的间距?

ad的component没有outline这一层,如何做?

不要带着其他软件的思想来搞AD哦 呵呵

ok。问题是,我如何控制器件间的距离?一定要依赖silkscreen?

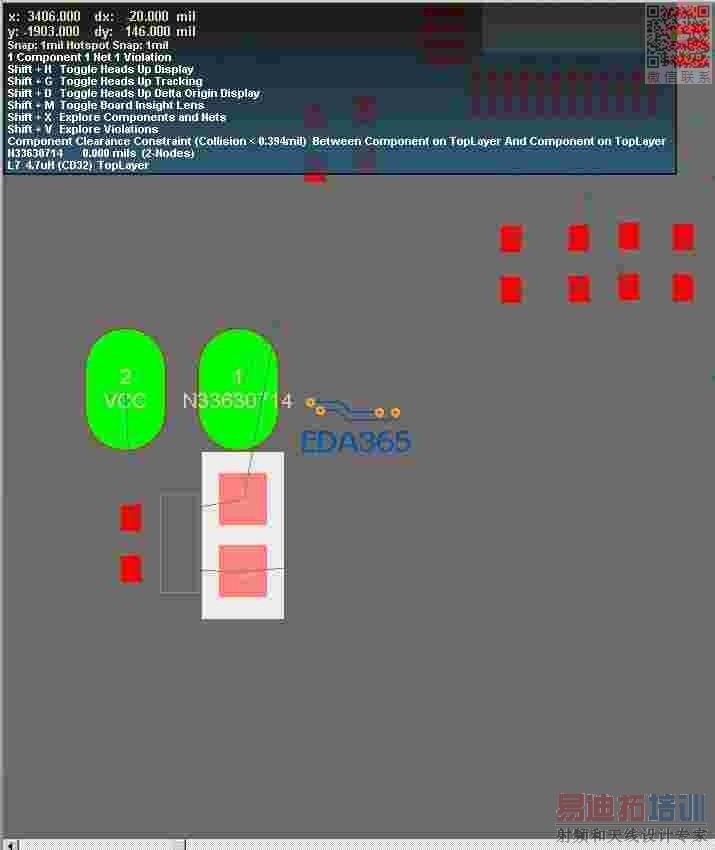

经研究发现,silk to silk clearance关掉之后,器件的大小不会改变,两个器件靠近了一样回报错(实际上是silkcreen靠的很近,pad相距很远很远)。

从网上看到一句话:Altium by default uses pads, polygons and everything on the silkscreen except designators and comments to define the component outline.

难道真的有这么愚蠢?

如果关掉了丝印间距规则的话...器件间距肯定是人为的控制咯...这样做起来很方便的..不过要小心出事故...

加标记的时候,不要在器件的库里加。而是在板上加。就不存在你说的问题了!

能不能截张图发上来看看...有关丝印间距报错的貌似只有丝印与丝印之间...丝印与PAD之间的两项规则...有可能是有别的问题引起报错..

好的!

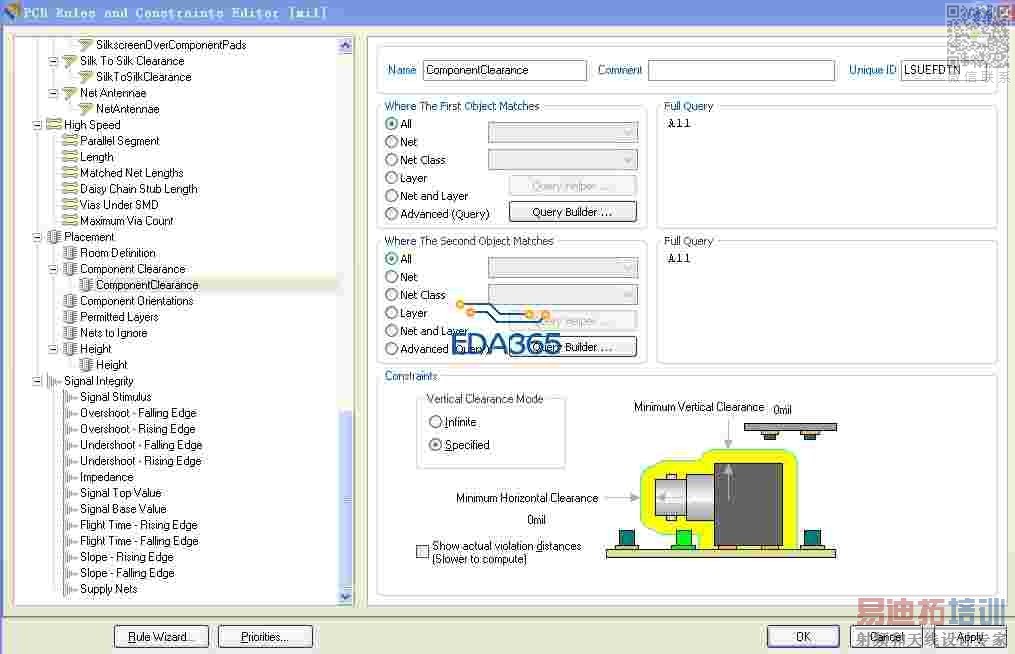

图片上不是说的很明显了么...是关于Component Clearance的间距规则导致的报错....

你按照图片设置下看看还会不会报错....

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:AD10导出结构图时椭圆孔有问题,请帮忙看看,

下一篇:T型等长如何做?