- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

AD9内电层plane负片如何去掉死铜

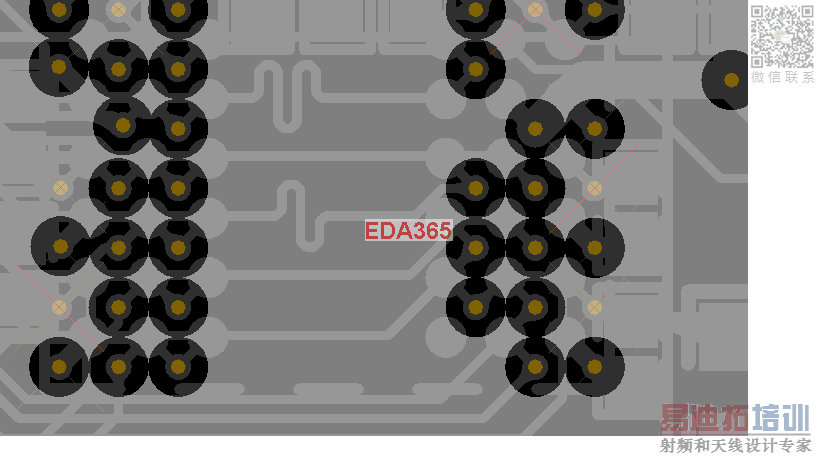

DRC检查提示内电层有大量的孤岛铜,但是不知道怎么删除,请各位大侠指点,非常感谢

DRC检查提示内电层有大量的孤岛铜,但是不知道怎么删除,请各位大侠指点,非常感谢

负片上看不到的是铜 你在那贴块铜就OK 相当于去掉了:)

如果確認是用的"PLANE"的話。那可以放FILL...LINE把這些你不用的地方去掉。負片嘛。走線的地方反而沒有銅。。

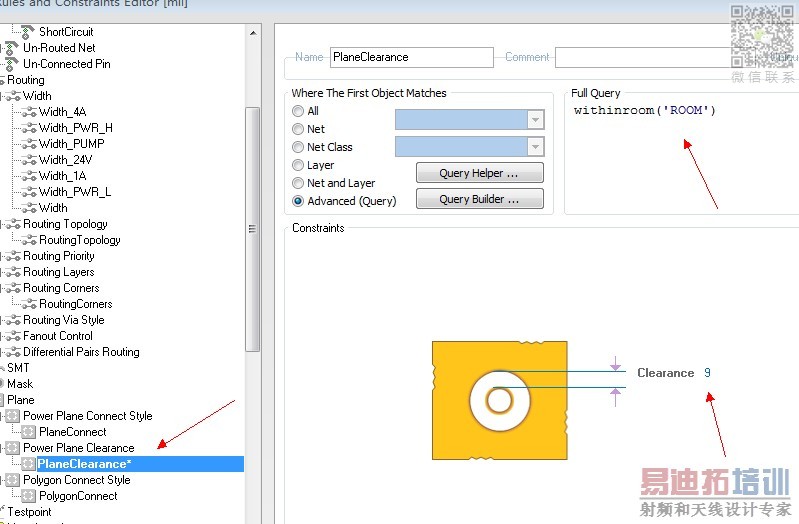

你可以将反焊盘设置小一点,放置ROOM,设置区域规则,如此设置

是的,在当前层PLACE-》FILL (或Solid Region) 就可以了。

pcb制造商没有设计问题反馈,软件此类规则检测信息提示应该不影响pcb制作,无需处理

我也遇到同样的问题,怎么解决呀?就是这种问题:Un-Routed Net Constraint ( (All) ):Isolated copper: Split Plane (DSP_CVDD) on InternalPlane3. Copper island connected to pads/vias detected. Copper area is : 1.6E2 sq. mils

DRC会报错的。

就安全间距接拉大!因为是内电层嘛!为什么不把间距接大呢?针对那些M-PDA完全可以的,这些PAD又不讲究什么偶合,回流之类的!

4楼的规则是如何完成,我现在就是想把GBA区域的负片层间距做小,其他地方拉大!如何建立规则!

这个设置值得参考

间距拉大可以解决部分问题只能这样讲,因为该平面层对应的信号引脚例如GND与非该层信号引脚例如1V是交错地分布的,把1V的间距拉大了,那些原本需要连起来的GND引脚就孤立了,这个间距需要合理设置

嗯,当初我也是见DRC报错才上来论坛请教的,不过后面两个厂家兴森快捷和广州杰赛科技反馈的问题列表里面并没有这一项,估计这种情况厂家会默认处理吧,于是我就觉得应该不算问题吧

四楼是正确的处理方法。

高速信号线要有完整的参考平面,这是出于信号完整性的考虑。

而PCB制造工厂,只考虑你文件是否符合制造工艺而已,他们不会帮你考虑设计问题的。

设计问题正是我们应该要考虑的。

后面确实把plane clearance设小了,解决了DRC报错的问题,当初出现铜孤岛使用的间距是12mil,跟polygon到信号的间距一样,后面改到10mil就不出现铜孤岛了,但实际上