- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

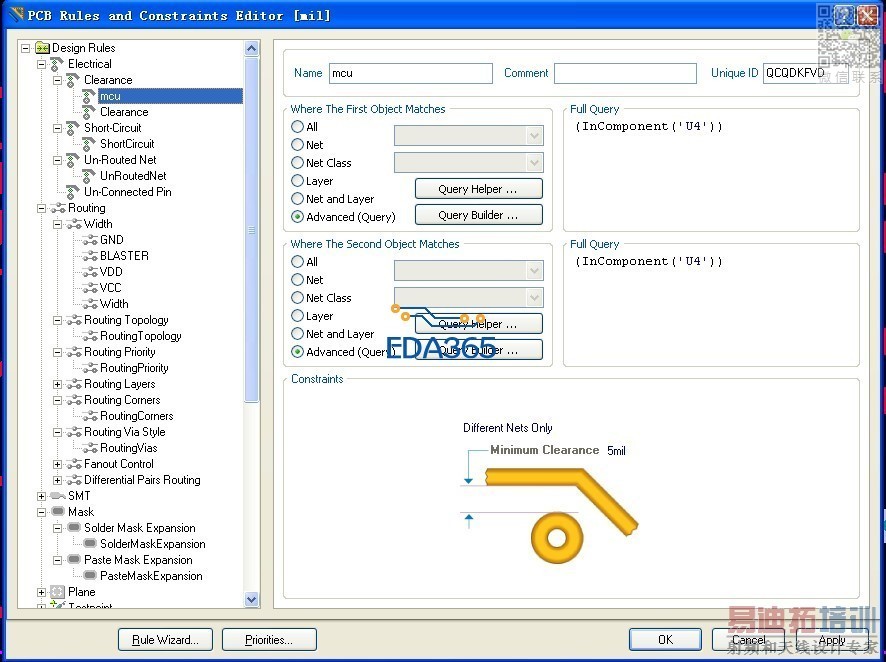

AD9如何设置器件引脚间距很小的设计规则?

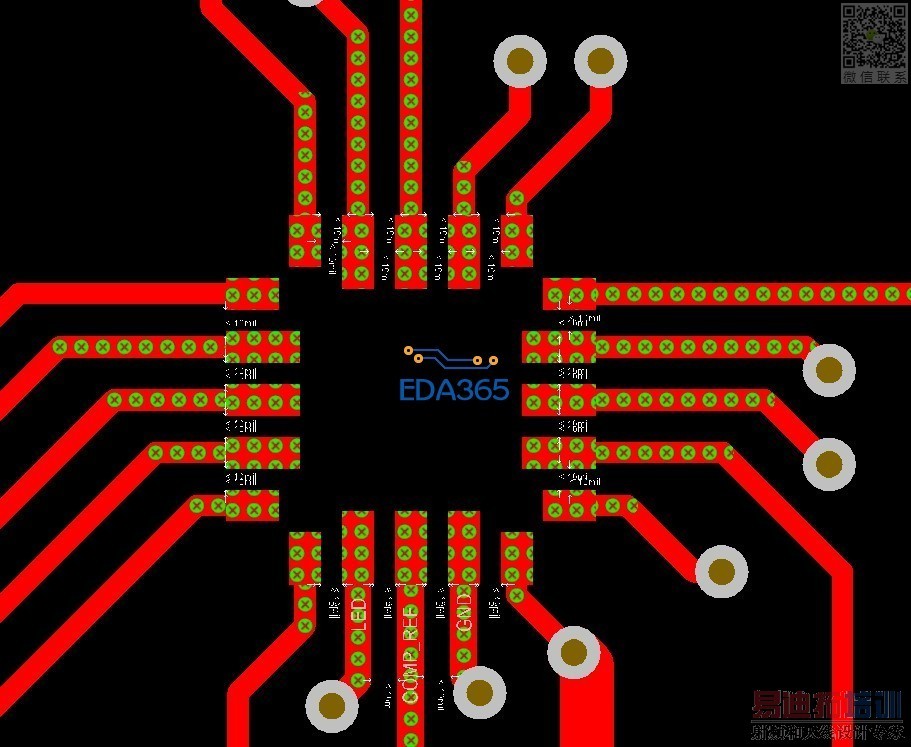

但布完线后,依然报间隔不条例规则。如下图:

哪里没有设置对呢?

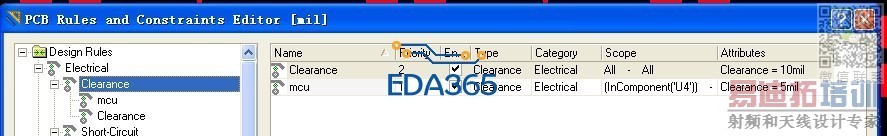

优先权设置成最高

MCU的间距规则优先级为1,默认的优先级为2。

谢谢你的回复,但问题没解决。

在MCU上盖一块ROOM

然后设置ROOM规则,比较方便

你设这个规则无非是为了看得时候不会报错,事实上你这个不是约束条件,所以,这一类的报错你不用管它

按照小编的设置应该也可以啊 为什么不行呢?我这里那样设置是可以实现的。

是不是间距比5mil还小啊?

知道是什么情况了 你的设置是对的,报错的不是器件管脚间距,是连到器件上的线间距报错了

其实你说的是这样的,我可以不理它的。但是还是想把问题搞清楚。

这也是一个好方法,我回头试试研究一下。

不是这样的,是这个单片机内部引脚间距小于10mil,我把内部规则设成5mil以后,布线时从引脚往外拉线,还是会报错的,只是不知道怎么把这种错误给它干掉。

哥们,对对对,就是这个意思,你是怎么设置的啊?快教教我。

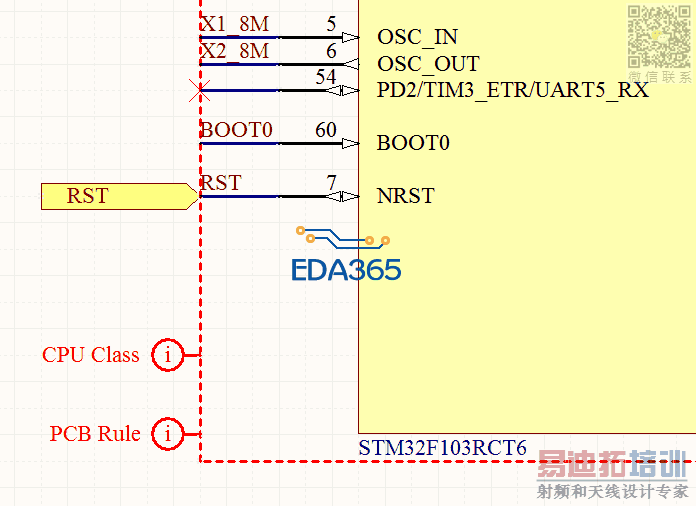

这类规则我一般在原理图中添加,点击放置->

Directives-> Blanket

->PCB Layout

->Net Class

添加网络类的好处在于不必更新过多的规格到PCB,这样你圈起来的网络都归属到一个类,CPU Class

注意执行检查时先把这种安全间距规则的enabled去掉,难免你圈起来的网络别的地方也有,都弄这么小的间距也不好。所以先检查其他的,最后只看到芯片周围线报警时,把这个enabled打开即可!

不要这么复杂,在PCB里可以直接添加class,具体做法是按D+C,新建一个class,在选择网络添加到这个class,就可以了。像这个报错,只要你的线宽比器件管脚窄,那就忽略它,没必要花这些不必要的时间,如果你硬是要改,那就把线与线的间距规则关掉,如果还是报错的话,你把所有到所有的最小间距改小。

如果都关掉不利于DRC检查好不好,你是一个一个添加方便,还是把原理图圈起来添加方便;真是搞不懂你?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:如何在W7安装AD09

下一篇:金手指与板框的报错怎么去掉?