- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

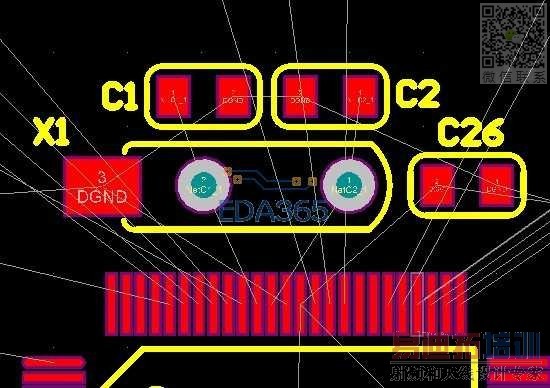

无法避免在晶振下面走线怎么办?

像你这样布局的话应该可以将信号线从TOP面往芯片内部引线打孔,再用BOTTOM层引线出去吧.

还有一点 我觉得你的C1 C2能放在晶振与电容之间最好,因为这两个电容主要有两个作用,一个是给从晶振流出的信号消除振荡效果,还有个作用就是给晶振起振的.现在的布局貌似第一个作用已经被弱化了.

你是说把C1和C2这两个电容往下面移动,放在晶振和芯片之间是吧?

对,这样从晶振流出的信号源就能优先经过电容的过滤,去除晶振信号中附带的振荡.对信号更好.

我认为不妥,电容还是在上面好,一般原理图都是那样,而且电容在前后都要靠与之连的地来整波

谢谢分享

时钟不要走过孔,加大,晶振电容和晶振单点接地。其他信号线远离晶振。

我认为吧,其实晶振的这个整波电容和一些电源的滤波退耦电容其意义都是一样的,我就是觉得从晶振流到芯片的信号,在流经过程中经过电容的整波,然后直接到芯片这样会好很多.就像滤波电容一样,最优设计就是先从电源管教直接流出到电容在从电容打孔或者拉线到主电源上,反之则滤波电容存在的意义不大.原理图的话,我也做过一些简单的,就晶振这块我也是这样话的,从芯片出来直接到晶振然后才到电容,因为我觉得这样方便,电容的地与晶振的地能用一个地标示就够了,PCB上我就不会这样处理了.还有就是应该不是说原理图上怎么定位器件PCB上也得怎么定位吧,有些硬件工程师做原理图还喜欢把一些芯片电源的滤波电容全部排成一排一起连起来放在芯片旁边,难道我们Layout在PCB上也要这样放么?呵呵 ,这都是一些个人见解,也不见得一定正确,呵呵.

按照三楼所说的布局,之后再走线,可以避免你说的情况

哈哈 我已经改过来啦,果然整个空间大了很多,不用晶振下面走线啦~~

我如果在晶振附近采用大面积敷铜,是不是也可以相当于单点接地?

大面积敷铜和单点接地不一样,所以在关键的信号上要采用单点接地。

謝謝分享

学习了。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:新手请教rule设置问题

下一篇:AD中Net label 与 port的区别