- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教 画PCB板时出现的一些问题

录入:edatop.com 点击:

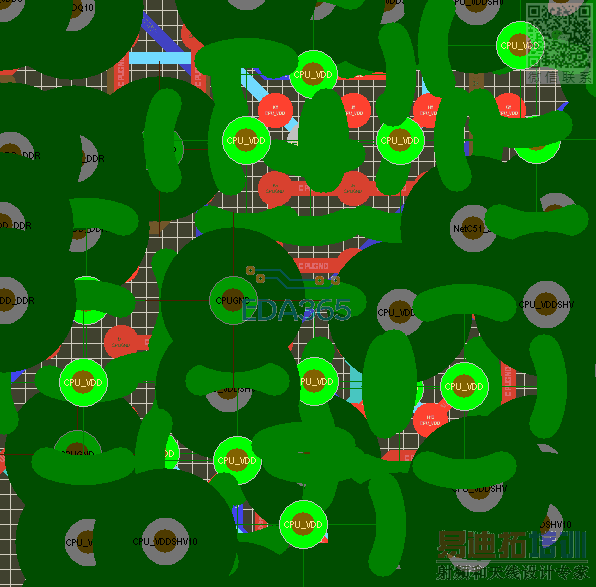

如图上所示,由于放置的过孔太多,导致VCC层中,相应网络不能连接起来。

这些管脚都是电源管脚,每个管脚都连接了一个去耦电容。

想问下各位,出现上述情况后,该怎么解决?

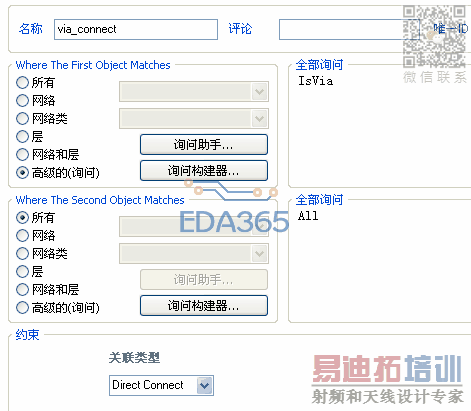

改一下规则吧,负片的过孔改为全连接,你现在是十字连接!

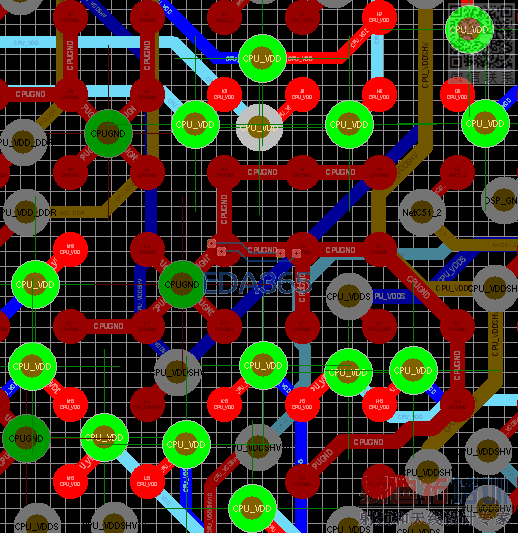

改了下规则,优先级设为最高,如上所示

但还是原来那样,仍然是十字连接。

如果平面層是負片的話。用這個。

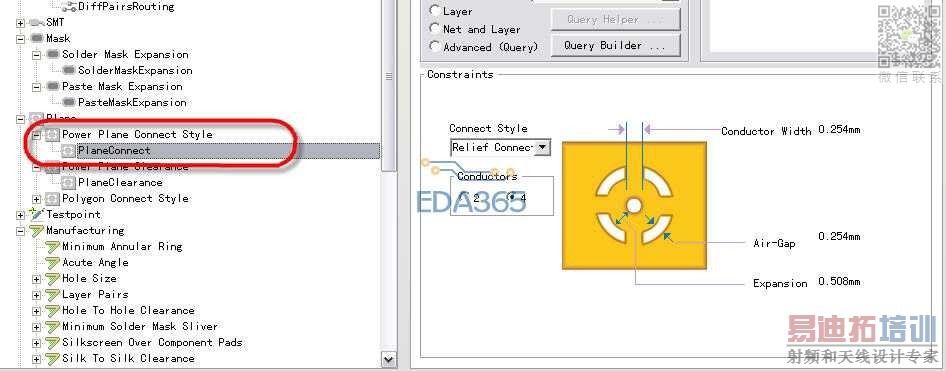

个人感觉BGA下边在负片中过孔与铜皮的距离可以再稍微改小一点,不然有些孔密集的地方就算将过孔改为全连接也还是会有这样的错误.

解决了,就是这个问题,谢谢!

过孔与铜皮的距离应该在哪儿设置?

找到,改小之后看着舒服很多

个人感觉BGA下边在负片中过孔与铜皮的距离可以再稍微改小一点

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:要的支持

下一篇:在AD中如何能像allegro那样做2倍,3倍线宽布线?