- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

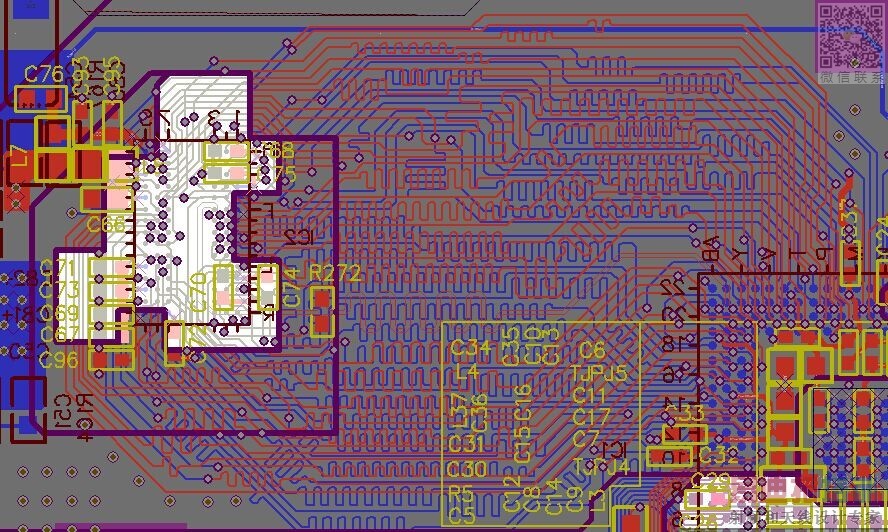

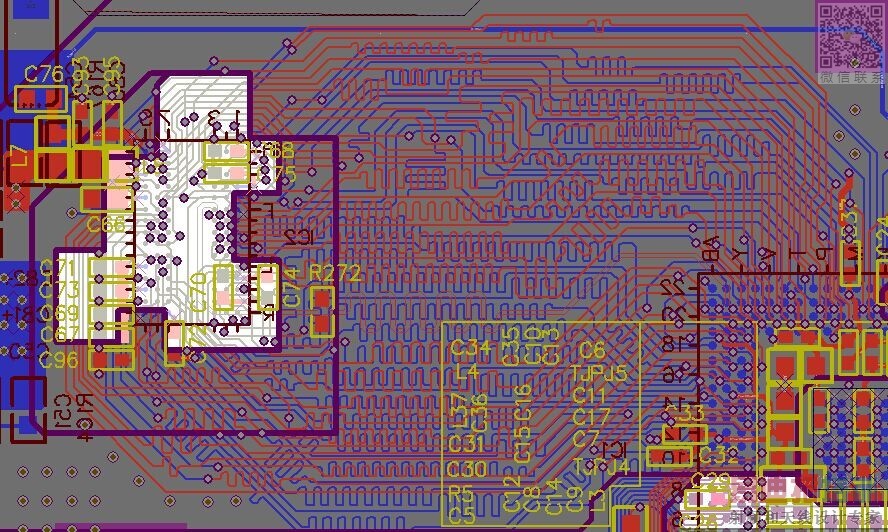

关于LPDDR走线跨分割的问题

录入:edatop.com 点击:

一片328PIN BGA 一片90PINLPDDR 16位地址线 32位数据线 还有一些控制线 四层板

高位数据一层 低位数据一层走底层

地址控制时钟走顶层

芯片放在底层 之前为了保护时钟和地址线 我选择了T/G/P/B的层叠 因为LPDDR内部有2个电源 总是要跨分割 不知道如何取舍?

之前有老师建议 地层靠近底层 然后顶层时钟线包地,这样地址就会垮分割。该如何做到两全其美,LPDDR时钟是133M,请各位大神,不吝赐教。

高位数据一层 低位数据一层走底层

地址控制时钟走顶层

芯片放在底层 之前为了保护时钟和地址线 我选择了T/G/P/B的层叠 因为LPDDR内部有2个电源 总是要跨分割 不知道如何取舍?

之前有老师建议 地层靠近底层 然后顶层时钟线包地,这样地址就会垮分割。该如何做到两全其美,LPDDR时钟是133M,请各位大神,不吝赐教。

又是没有人回复

又是没有人回复

厉害

加层

本来是6层 现在改成4层的 节省成本好么

节省成本与信号质量那个更重要呢》?不要盲目的节省成本

一个电源用平面,一个电源用走线。

有时其实说得挺玄的,跨一下分割也不至于说就不正常工作了。

正常工作啊 只是EMC没有通过 改了叠层以后就通过了的

?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:AD16导入STEP文件没颜色

下一篇:AD9在原理图中能设置差分线吗