- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

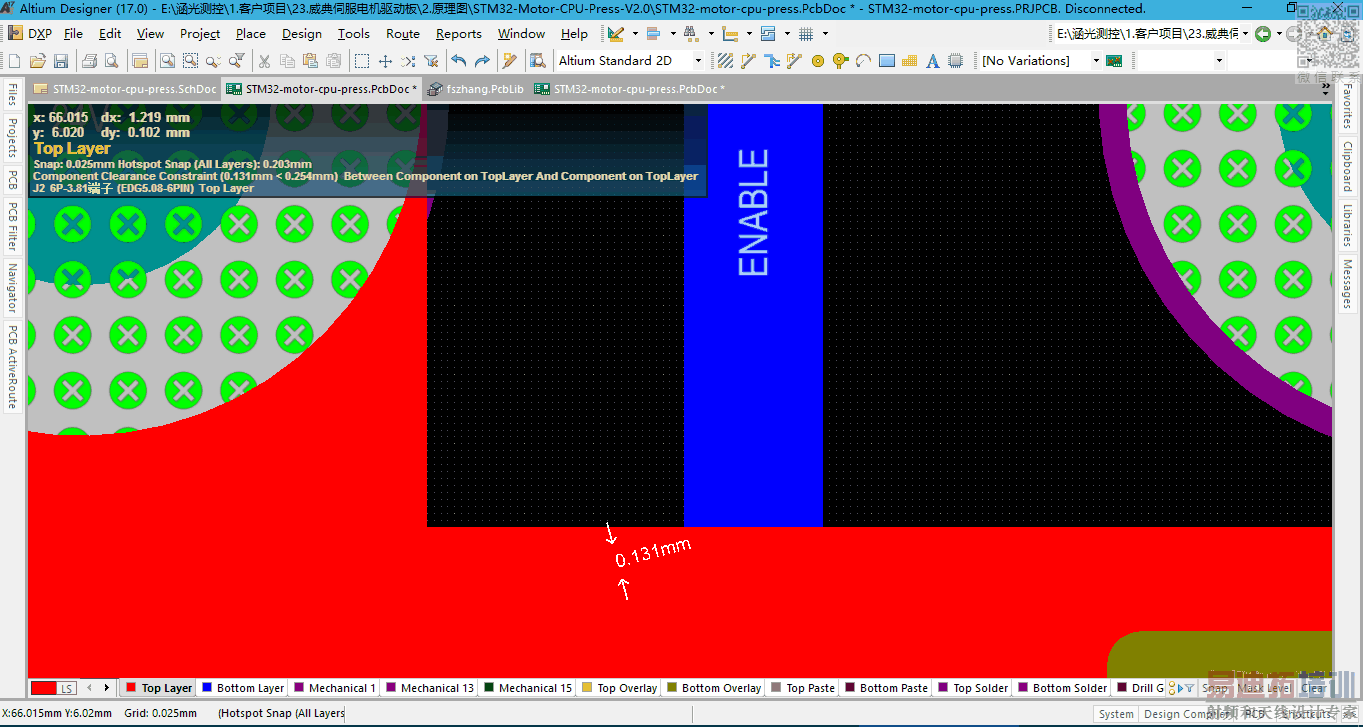

AD17生成PCB后报错,如下图片,求指教

录入:edatop.com 点击:

原理图生成PCB后,个别元器件的封装会报错,如下图片,求大虾指教。

请教一下这是什么问题,因为封装之前用是没问题的。

从左上角的信息来看,是你顶层的两个元件太近了,只有0.131mm,而你规则里设置的是0.254mm。

你将部分焊盘画在了封装里,放置的时候,焊盘部分靠的太近,可能你的本意是两个过孔之间同网络的焊盘,结果软件识别成2个元器件靠的太近已经超过了你的规则规定,所以报错。

是这样的,我昨天看了一下原理图,原本有6个固定孔,但是生成PCB后,只有4个(最初不是我从原理图更新到PCB的),报错的地方就是缺失定位孔中的一个,不知道为什么变的那么小,在同一个面,软件就认为小于安全距离了,所以报错,把原来的不用的那两个定位孔删除,更新一下PCB就好了,不过还是谢谢。

17用着怎么样

还可以,我用的17.0.11这个版本,基本没什么问题。

我是自学的 真他么累

学习啦啦啦啦 啦啦啦

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Altum Designer 09 怎么打开local documents

下一篇:请教各位,关于位号的批量修改问题