- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

郁闷的EE2007,准备用EE2007中的DXD画原理图的XDJM,请暂缓你的脚步

看到MENTOR更新了,我也与时俱进,用上EE2007,更新到OCRU2.

测试时,单页的图纸,没有出任何问题,感觉很好。

不久前做一个工程,要用层次图画原理图,刚开始一切都很正常。顺利地导入了PCB,布局,一切都是那么美好!

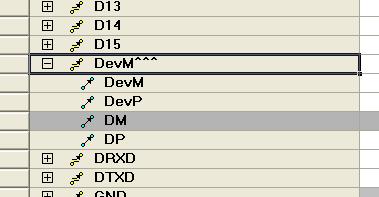

然而,在分配网络类表时,发现了有地址线A0不见了(连在了A2下面),DevM,DevP,DM,DP也连在一起。不会吧?进入PCB

看了一下,还真是这样。

?这是怎么回事?

回头仔细查找网络,并显式标注了各个网络名,一切都正常。至少,从原理图上来看是没有任何问题。

把所有的连接都删除,然后逐条添加,随时查看CES,发现只要把下面红圈中的DM连上,就会出问题,

删除相关元件也没有用。重新生成Symbol,重开软件,重启,都没用。

再查CES,类似的连接还有。这样的图纸根本上没有用!

唉,用EE2007画的原理图,现在还没有发现它还有剩余价值可以利用。

郁闷,失望,也有点难过。

难道,一切都只能重来?

删除CES

删除CES,然后重新设置CES试试看。

根目录-》CES

根目录-》PCB->LAYOUT->CES

小编,那是你理解错了。

这是Mentor最新的,把经过阻容元件的网络自动形成一个组网络名,这样对信号归类非常简单,使用一个网络名归入一个例如规则内,不用每个段都去操作一次。

这个功能在2005中就有了。

要解决则很简单,将组名后的Analog钩上,网络名就分开了。

但是EE2007有个很不好的问题,就是设计文件格式不明了了,如果使用中文,则一旦出了问题没法修复了。所以EE2007原理图不要使用中文。2005中可以修复。

2007功能很强,较2005有较大的进步,但是iod的集成反而倒退了,不知为什么。

没有用过EE2007,不是很明白

对于楼上所说的iod集成没有概念,哪位知道的能讲讲么?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:画好原理图,创建PCB文件时提示:you cannot create a PCB from this foreign ICDB

下一篇:Mentor 布局等间距如何设置