- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

麻烦大了,请关注

可是试了很多方法都不行,“CES”也试了一下,还是不奏效。主要是自己没有经验,不懂。

有没有热心的同行,提供一个解决问题的方法,或者帮忙转成PADS9.0以下的版本。让我好交差!如果这项目不能按时完成,可能要提前回家过年了,希望高抬贵手,谢谢了!

自己顶!

帮顶!高手出来答下

大家来顶一下。

你发过來帮你试試,但先声名不一定成!

tmlee@163.com

文件已经发送,文件名“ExportDesignData.rar”,谢谢!

请顺便告知是什么原因造成的

是不是pin to pin的规则设得太大了,或者是线间距,看看

“Restricted Layer Rule Violstion”

一般是规则设置问题。

谢谢以上好朋友!

我正在试,还没有找到原因,有个问题我是这样解决哦的:

如果线路之间有电阻,那么我先把电阻移近连接端的一边把线连上,然后再把元件移连接端的另外一边把线连上,再把元件挪到适当的位置,大家是不是觉得很搞笑呢!就是用这种土办法我把很多连不起来的走线连好了。

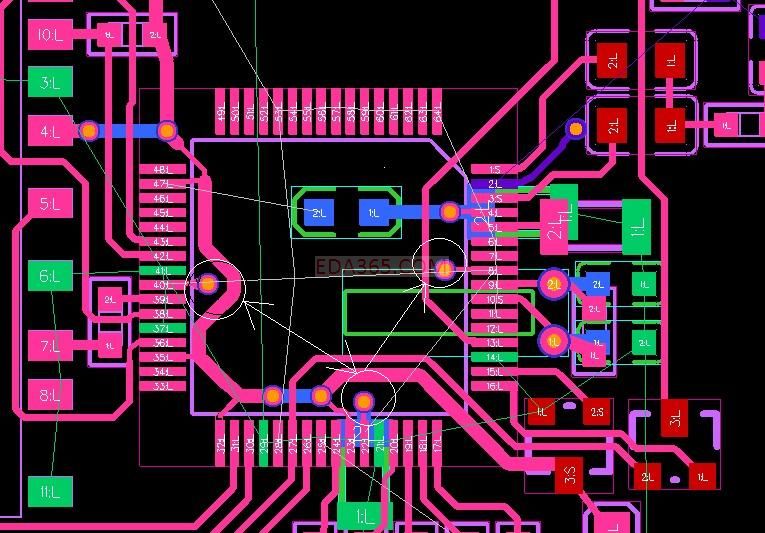

现在剩下的问题是连线之间没有元件,如IC和IC之间没有办法移动的,如图:白色圆圈和白色箭头处。想不出招数了。

朋友们能不能再支招?或者土办法也行。

EE2005 应该能打开吧? 我明天去公司可以帮你看看 现在机子上还没装

mikle517@163.com

EE2007.5版本的,可以吗?

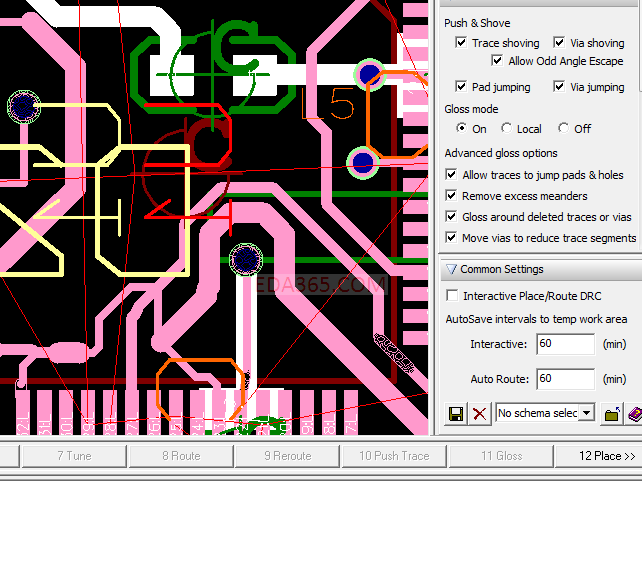

你可以先把 interactive place/route drc 关了,弄上了再开,那很多不能移动和连接的都可以弄,但是要小心因為沒有 drc 很容易连錯,所以 drc 经常提示“Restricted Layer Rule Violstion” 但不一定是是錯的,

tmlee:邮件已经收到,虽然丢失了焊盘,但是可以解决问。

方法实用,我试了一下。 谢谢,太感谢了!

希望你不用提前回家过年

因为软件技术性的延误,可能要延后回家过年了

如果项目不是很复杂,那还是换回去把

我自己也是,原来用2005的,后来想拿2007作一个新的项目,作是作完了,但是还是比预想的慢了一半时间

替小编谢谢tmlee

你的nets有設置繞在特定layer的要求

你的版本好高呀

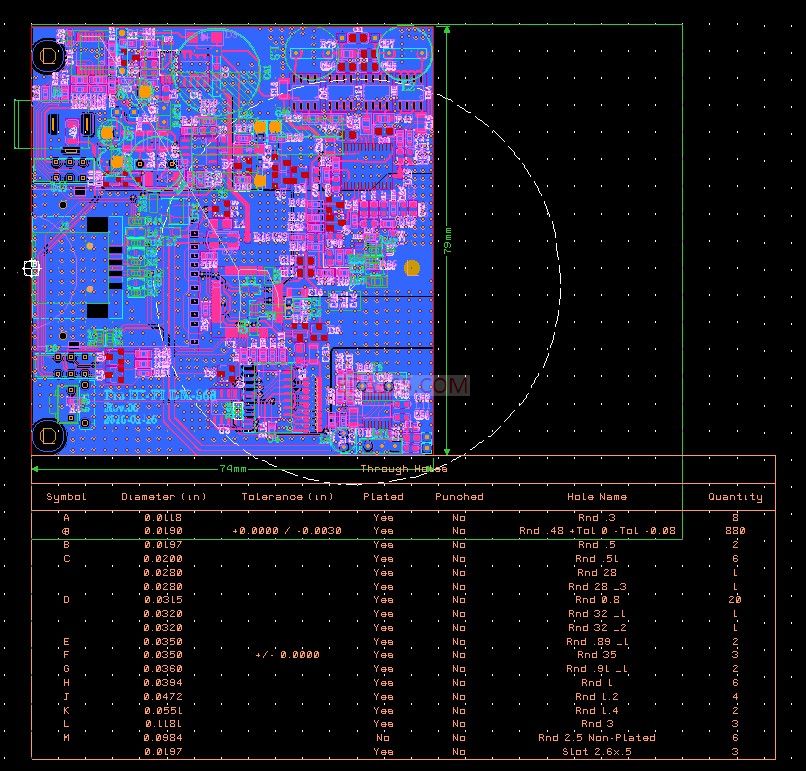

谢谢tmlee !谢谢以上朋友们,今天终于把项目做完,刚发出去做板。

除了以上走线外,接下来的敷铜(当然包括分割了),产生丝印,输出Gerber都是很考验人的技术,我是一边骂一边完成的,差不多可以说这项目是骂出来的。

闲话少说,上图和大家分享一下:

接下来就是一一解决遇到的问题了,唉,有个高手指点一下能省多少功夫啊!

恭喜!祝你新年快乐,恭喜發大財,你老家在那里呢?

老家,广东的,现在人在深圳

参考以下几点解决:

1;Editor Control > Routes Tab-Route Settings:Allow One Additional Via per SMD Pin 此处勾选

2;Editor Control > Routes Tab-Route Settings:Use Place Outlines as Via Obstructs 此处不勾选

3;Editor Control > Pad Entry-Allow Vias Under Pads 此处都勾选(每种焊盘皆需要勾选)

4;Editor Control >走线时 Grids 全部设置为0试试。

5;Setup > Net Properties or Design Capture > Tools > Net Properties暂时清除卸载所有规则

6;Net Classes and Clearances > Nets Tab暂时清除卸载所有规则

LZ这个使用“CTRL-E”取消“prevent loop”选项即可。

这个选项是防止你的连线“环回”用的。一般在模拟电路里是不允许电路环回的。数字电路刚好相反!

取消后就能随意按自己的需要顺序连线了。