- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DRC检查问题

录入:edatop.com 点击:

DRC - (Final DRC)

-----------------

08:00 AM Tuesday, September 09, 2008

Job Name: D:\prj\080906\PCB\22V1.0.pcb

---------

PROXIMITY

---------

Use DRC Window : NO

Disable Same Cell Pad-Pad Checks : NO

Enable Same Net Pad-Pad Checks : NO

Layers Specifed To Check : Layer 1

Layer 2

Net Class Clearances And Rules

------------------------------

>> Components Top TO Components Top

Hazards Found : 4

Traces Layer 1 TO Traces Layer 1

No Hazards.

Traces Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Traces Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Traces Layer 1 TO Part Holes Layer 1

No Hazards.

Traces Layer 1 TO Via Pads Layer 1

No Hazards.

Traces Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Holes Layer 1

No Hazards.

Part Holes Layer 1 TO Via Pads Layer 1

No Hazards.

Part Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Via Pads Layer 1 TO Via Pads Layer 1

No Hazards.

Via Pads Layer 1 TO Via Holes Layer 1

No Hazards.

Via Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Traces Layer 2 TO Traces Layer 2

No Hazards.

Traces Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Traces Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Traces Layer 2 TO Part Holes Layer 2

No Hazards.

Traces Layer 2 TO Via Pads Layer 2

No Hazards.

Traces Layer 2 TO Via Holes Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Via Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Holes Layer 2

No Hazards.

Part Holes Layer 2 TO Via Pads Layer 2

No Hazards.

Part Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Via Pads Layer 2 TO Via Pads Layer 2

No Hazards.

Via Pads Layer 2 TO Via Holes Layer 2

No Hazards.

Via Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Total Hazards Found : 4

Planes Clearances And Rules

---------------------------

Positive Planes Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Holes Layer 1

No Hazards.

Positive Planes Layer 1 TO Positive Planes Layer 1

No Hazards.

Positive Planes Layer 1 TO Route Border

No Hazards.

Positive Planes Layer 1 TO Traces Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Pads Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Holes Layer 1

No Hazards.

Positive Planes Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Holes Layer 2

No Hazards.

Positive Planes Layer 2 TO Route Border

No Hazards.

Positive Planes Layer 2 TO Traces Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Pads Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Holes Layer 2

No Hazards.

Total Hazards Found : 0

Non-Net Class Element To Element Clearances And Rules

-----------------------------------------------------

Route Border TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 1 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 1 Clearance: 0mm

No Hazards.

>> Board Outline TO Placement Outlines Top Clearance: 0.15mm

Hazards Found : 2

Board Outline TO Part Pads SMD Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 2 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Bottom Clearance: 0.15mm

No Hazards.

Board Outline TO Part Pads SMD Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 2 Clearance: 0mm

No Hazards.

Total Hazards Found : 2

Total Proximity Hazards Found : 6

----------------------------

CONNECTIVITY & SPECIAL RULES

----------------------------

Check For Unplaced Parts : YES

No Hazards.

Check For Missing Parts : YES

No Hazards.

Check Trace Hangers : YES

No Hazards.

Check Trace Loops : YES

No Hazards.

Check Trace Widths : YES

Hazards Found : 122

Check Single Point Nets : YES

Hazards Found : 1

Check NonPlane Unrouted/Partially Routed Nets : YES

No Hazards.

Check Plane Unrouted/Partial Routed Nets : YES

No Hazards.

Check Routed Plane Pins : YES

No Hazards.

Check Plane Islands : YES

No Hazards.

Check Dangling Vias/Jumpers : YES

No Hazards.

Check Unrouted Pins : YES

No Hazards.

Check Routed Non-Plated Pins : YES

No Hazards.

Check Minimum Annular Ring : NO

Check For Vias Under SMD Pads : YES

No Hazards.

Check For Vias Under Top Place Outlines : YES

Hazards Found : 52

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 10

Check For Missing Conductive Pads : NO

Check For Missing Part Soldermask Pads : NO

Check For Missing Via Soldermask Pads : NO

Check For Missing Solderpaste Pads : NO

Total Connectivity/SpecialRules Hazards Found : 185

====================================================================

Total DRC Hazards Found : 191

08:00 AM Tuesday, September 09, 2008

以上是我做的板子的DRC结果,

Check For Vias Under Top Place Outlines : YES

Hazards Found : 52

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 10

其中元件的放置框内打孔有报错,怎么能让它不报错呢?

-----------------

08:00 AM Tuesday, September 09, 2008

Job Name: D:\prj\080906\PCB\22V1.0.pcb

---------

PROXIMITY

---------

Use DRC Window : NO

Disable Same Cell Pad-Pad Checks : NO

Enable Same Net Pad-Pad Checks : NO

Layers Specifed To Check : Layer 1

Layer 2

Net Class Clearances And Rules

------------------------------

>> Components Top TO Components Top

Hazards Found : 4

Traces Layer 1 TO Traces Layer 1

No Hazards.

Traces Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Traces Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Traces Layer 1 TO Part Holes Layer 1

No Hazards.

Traces Layer 1 TO Via Pads Layer 1

No Hazards.

Traces Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Holes Layer 1

No Hazards.

Part Holes Layer 1 TO Via Pads Layer 1

No Hazards.

Part Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Via Pads Layer 1 TO Via Pads Layer 1

No Hazards.

Via Pads Layer 1 TO Via Holes Layer 1

No Hazards.

Via Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Traces Layer 2 TO Traces Layer 2

No Hazards.

Traces Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Traces Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Traces Layer 2 TO Part Holes Layer 2

No Hazards.

Traces Layer 2 TO Via Pads Layer 2

No Hazards.

Traces Layer 2 TO Via Holes Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads SMD Layer 2 TO Via Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Holes Layer 2

No Hazards.

Part Holes Layer 2 TO Via Pads Layer 2

No Hazards.

Part Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Via Pads Layer 2 TO Via Pads Layer 2

No Hazards.

Via Pads Layer 2 TO Via Holes Layer 2

No Hazards.

Via Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Total Hazards Found : 4

Planes Clearances And Rules

---------------------------

Positive Planes Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Holes Layer 1

No Hazards.

Positive Planes Layer 1 TO Positive Planes Layer 1

No Hazards.

Positive Planes Layer 1 TO Route Border

No Hazards.

Positive Planes Layer 1 TO Traces Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Pads Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Holes Layer 1

No Hazards.

Positive Planes Layer 2 TO Part Pads SMD Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Holes Layer 2

No Hazards.

Positive Planes Layer 2 TO Route Border

No Hazards.

Positive Planes Layer 2 TO Traces Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Pads Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Holes Layer 2

No Hazards.

Total Hazards Found : 0

Non-Net Class Element To Element Clearances And Rules

-----------------------------------------------------

Route Border TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 1 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 1 Clearance: 0mm

No Hazards.

>> Board Outline TO Placement Outlines Top Clearance: 0.15mm

Hazards Found : 2

Board Outline TO Part Pads SMD Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 2 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Bottom Clearance: 0.15mm

No Hazards.

Board Outline TO Part Pads SMD Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 2 Clearance: 0mm

No Hazards.

Total Hazards Found : 2

Total Proximity Hazards Found : 6

----------------------------

CONNECTIVITY & SPECIAL RULES

----------------------------

Check For Unplaced Parts : YES

No Hazards.

Check For Missing Parts : YES

No Hazards.

Check Trace Hangers : YES

No Hazards.

Check Trace Loops : YES

No Hazards.

Check Trace Widths : YES

Hazards Found : 122

Check Single Point Nets : YES

Hazards Found : 1

Check NonPlane Unrouted/Partially Routed Nets : YES

No Hazards.

Check Plane Unrouted/Partial Routed Nets : YES

No Hazards.

Check Routed Plane Pins : YES

No Hazards.

Check Plane Islands : YES

No Hazards.

Check Dangling Vias/Jumpers : YES

No Hazards.

Check Unrouted Pins : YES

No Hazards.

Check Routed Non-Plated Pins : YES

No Hazards.

Check Minimum Annular Ring : NO

Check For Vias Under SMD Pads : YES

No Hazards.

Check For Vias Under Top Place Outlines : YES

Hazards Found : 52

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 10

Check For Missing Conductive Pads : NO

Check For Missing Part Soldermask Pads : NO

Check For Missing Via Soldermask Pads : NO

Check For Missing Solderpaste Pads : NO

Total Connectivity/SpecialRules Hazards Found : 185

====================================================================

Total DRC Hazards Found : 191

08:00 AM Tuesday, September 09, 2008

以上是我做的板子的DRC结果,

Check For Vias Under Top Place Outlines : YES

Hazards Found : 52

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 10

其中元件的放置框内打孔有报错,怎么能让它不报错呢?

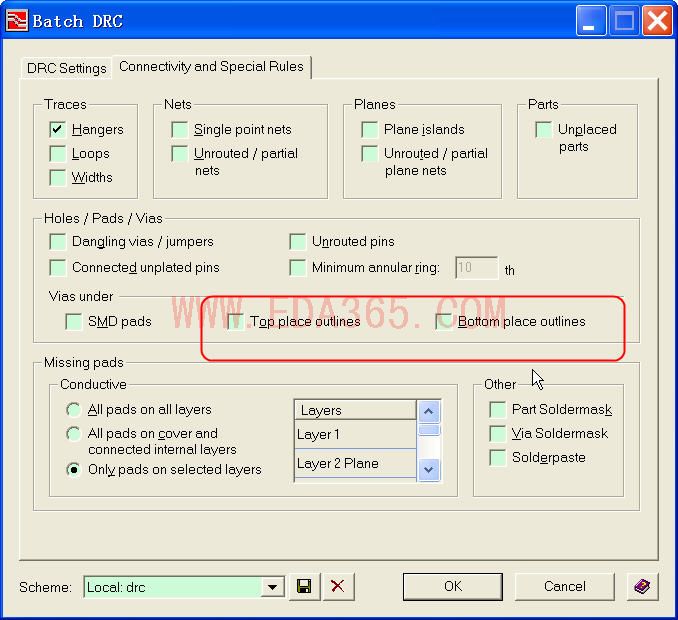

如 下 图

谢谢小编,问题得到解决了!

原来是可以设置的,线宽也可以设置不报错呢!