- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

EE7.9.4铺铜后 batch DRC检查

录入:edatop.com 点击:

DRC - (Final DRC)

-----------------

04:46 PM Thursday, April 16, 2015

Job Name: E:\WorkSpace\Doppler\Hardware\DS120\PCB\Board1.pcb

---------

PROXIMITY

---------

Use DRC Window : NO

Disable Same Cell Pad-Pad Checks : NO

Enable Same Net Pad-Pad Checks : NO

Layers Specifed To Check : Layer 1

Layer 2

Layer 3

Layer 4

Net Class Clearances And Rules

------------------------------

Components Layer 1 TO Components Layer 1

No Hazards.

Traces Layer 1 TO Traces Layer 1

No Hazards.

Traces Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Traces Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Traces Layer 1 TO Part Holes Layer 1

No Hazards.

Traces Layer 1 TO Via Pads Layer 1

No Hazards.

Traces Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Holes Layer 1

No Hazards.

Part Holes Layer 1 TO Via Pads Layer 1

No Hazards.

Part Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Via Pads Layer 1 TO Via Pads Layer 1

No Hazards.

Via Pads Layer 1 TO Via Holes Layer 1

No Hazards.

Via Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Holes Layer 2

No Hazards.

Part Holes Layer 2 TO Via Pads Layer 2

No Hazards.

Part Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Via Pads Layer 2 TO Via Pads Layer 2

No Hazards.

Via Pads Layer 2 TO Via Holes Layer 2

No Hazards.

Via Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Traces Layer 3 TO Traces Layer 3

No Hazards.

Traces Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Traces Layer 3 TO Part Holes Layer 3

No Hazards.

Traces Layer 3 TO Via Pads Layer 3

No Hazards.

Traces Layer 3 TO Via Holes Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Part Holes Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Via Pads Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Via Holes Layer 3

No Hazards.

Part Holes Layer 3 TO Via Pads Layer 3

No Hazards.

Part Holes Layer 3 TO Via Holes Layer 3

No Hazards.

Via Pads Layer 3 TO Via Pads Layer 3

No Hazards.

Via Pads Layer 3 TO Via Holes Layer 3

No Hazards.

Via Holes Layer 3 TO Via Holes Layer 3

No Hazards.

Components Layer 4 TO Components Layer 4

No Hazards.

Traces Layer 4 TO Traces Layer 4

No Hazards.

Traces Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Traces Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Traces Layer 4 TO Part Holes Layer 4

No Hazards.

Traces Layer 4 TO Via Pads Layer 4

No Hazards.

Traces Layer 4 TO Via Holes Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Holes Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Via Pads Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Via Holes Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Part Holes Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Via Pads Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Via Holes Layer 4

No Hazards.

Part Holes Layer 4 TO Via Pads Layer 4

No Hazards.

Part Holes Layer 4 TO Via Holes Layer 4

No Hazards.

Via Pads Layer 4 TO Via Pads Layer 4

No Hazards.

Via Pads Layer 4 TO Via Holes Layer 4

No Hazards.

Via Holes Layer 4 TO Via Holes Layer 4

No Hazards.

Total Hazards Found : 0

Planes Clearances And Rules

---------------------------

Positive Planes Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Holes Layer 1

No Hazards.

Positive Planes Layer 1 TO Positive Planes Layer 1

No Hazards.

Positive Planes Layer 1 TO Route Border

No Hazards.

Positive Planes Layer 1 TO Traces Layer 1

No Hazards.

Positive Planes Layer 1 TO Plane Obstructs Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Pads Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Holes Layer 1

No Hazards.

Positive Planes Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Holes Layer 2

No Hazards.

Positive Planes Layer 2 TO Route Border

No Hazards.

Positive Planes Layer 2 TO Via Pads Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Holes Layer 2

No Hazards.

Positive Planes Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Positive Planes Layer 3 TO Part Holes Layer 3

No Hazards.

Positive Planes Layer 3 TO Positive Planes Layer 3

No Hazards.

Positive Planes Layer 3 TO Route Border

No Hazards.

Positive Planes Layer 3 TO Traces Layer 3

No Hazards.

Positive Planes Layer 3 TO Trace Obstructs Layer 3

No Hazards.

Positive Planes Layer 3 TO Via Pads Layer 3

No Hazards.

Positive Planes Layer 3 TO Via Holes Layer 3

No Hazards.

Positive Planes Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Positive Planes Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Positive Planes Layer 4 TO Part Holes Layer 4

No Hazards.

Positive Planes Layer 4 TO Positive Planes Layer 4

No Hazards.

Positive Planes Layer 4 TO Route Border

No Hazards.

Positive Planes Layer 4 TO Traces Layer 4

No Hazards.

Positive Planes Layer 4 TO Plane Obstructs Layer 4

No Hazards.

Positive Planes Layer 4 TO Via Pads Layer 4

No Hazards.

Positive Planes Layer 4 TO Via Holes Layer 4

No Hazards.

Total Hazards Found : 0

Non-Net Class Element To Element Clearances And Rules

-----------------------------------------------------

Route Border TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 1 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Layer 1 Clearance: 0.25mm

No Hazards.

Board Outline TO Part Pads SMD Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Part Pads Thru Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 2 Clearance: 0mm

No Hazards.

>> Via Obstructs Layer 3 TO Via Pads Layer 3 Clearance: 0mm

Hazards Found : 6

>> Via Holes Layer 3 TO Via Obstructs Layer 3 Clearance: 0mm

Hazards Found : 6

>> Traces Layer 3 TO Trace Obstructs Layer 3 Clearance: 0mm

Hazards Found : 1

Route Border TO Via Pads Layer 3 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 3 Clearance: 0mm

No Hazards.

Part Pads Thru Layer 3 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 3 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 4 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 4 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 4 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 4 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Layer 4 Clearance: 0.25mm

No Hazards.

Board Outline TO Part Pads SMD Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 4 Clearance: 0mm

No Hazards.

Total Hazards Found : 13

Total Proximity Hazards Found : 13

----------------------------

CONNECTIVITY & SPECIAL RULES

----------------------------

Check For Unplaced Parts : YES

No Hazards.

Check For Missing Parts : YES

No Hazards.

Check EP Component Hazards : YES

No Hazards.

Check Trace Hangers : YES

No Hazards.

Check Trace Loops : YES

No Hazards.

Check Trace Widths : YES

No Hazards.

Check Single Point Nets : NO

Check NonPlane Unrouted/Partially Routed Nets : YES

No Hazards.

Check Plane Unrouted/Partial Routed Nets : YES

No Hazards.

Check Routed Plane Pins : YES

No Hazards.

Check Plane Islands : YES

No Hazards.

Check Dangling Vias/Jumpers : YES

No Hazards.

Check Unrouted Pins : YES

No Hazards.

Check Routed Non-Plated Pins : YES

No Hazards.

Check Minimum Annular Ring : NO

Check For Vias Under SMD Pads : YES

No Hazards.

Check For Vias Under Top Place Outlines : YES

Hazards Found : 25

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 11

Check For Missing Conductive Pads : NO

Check For Missing Part Soldermask Pads : NO

Check For Missing Via Soldermask Pads : NO

Check For Missing Solderpaste Pads : NO

Total Connectivity/SpecialRules Hazards Found : 36

====================================================================

Total DRC Hazards Found : 49

04:46 PM Thursday, April 16, 2015

高手帮忙看看这个DRC是否有什么问题? 我看板卡上没哟问题啊。 但是drc报告有49处警告!

你要去找怎么定位每一个DRC冲突的位置,自己一个个去找,这个报告没用的

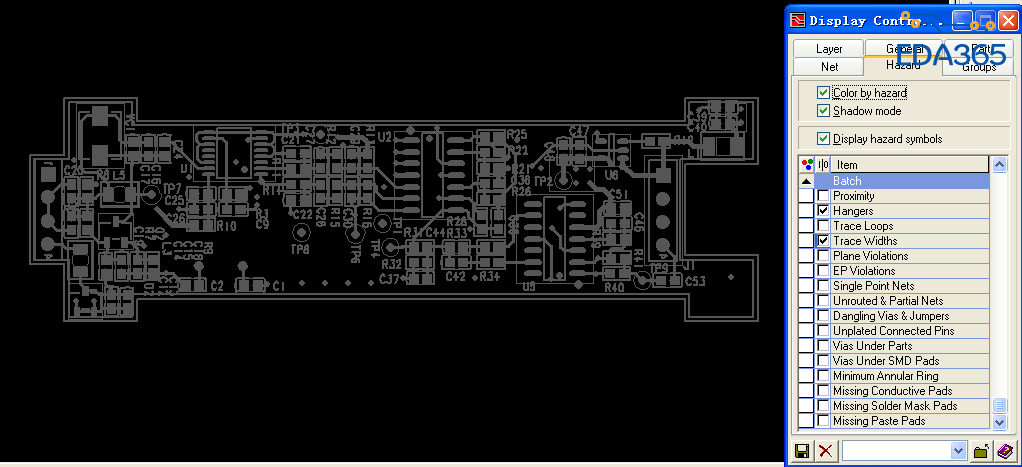

batch drc 之后又hazard view,里面#刷新一下了一个个查

已经看不到有白色的警告线了。 但是还是提示有49处 hanzards 。

问题在这里。 不知道是什么意思!

你这两个地方写的很清楚了。第一个是间距错误,就是一个叫VIA OBSTRUCT的区域和你的VIA靠太近了,具体在哪里要你自己一个个去点击查看,看VIA OBSTRUCT在哪里。

第二个是VIA UNDER PARTS问题,就是你设置了器件下面不能打孔,这个违反规则了,具体在哪里设要自己去找一找。

另外我想说,第二个规则其实没必要去修改,违反就违反了,你可以选择接受,就是accept,没有那么完美的DRC,这个和其他软件有区别,我们有时候出板几千个DRC,但是只要重点的没有违反,其余的warnning就Accept了,当然你得知道是Accept的是什么。

你看不到DRC指示是因为你左边把那些显示的勾去掉了。