- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DRC没错,但是却不能生成网络表?

用orcad画了一个电路图,经过修改DRC终于没有错了,但是生成网络表时却出现了错误,信息如下:

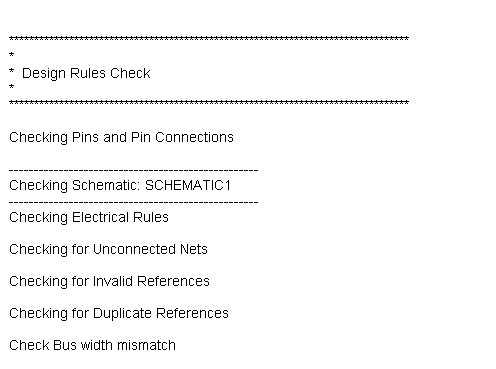

DRC时的信息:

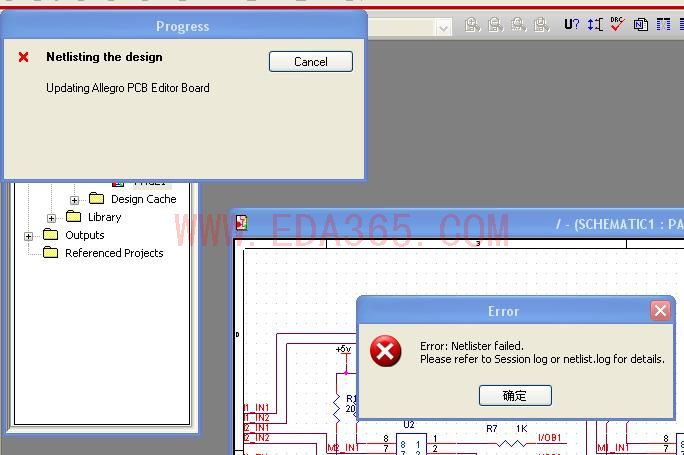

生成网络表时的信息:

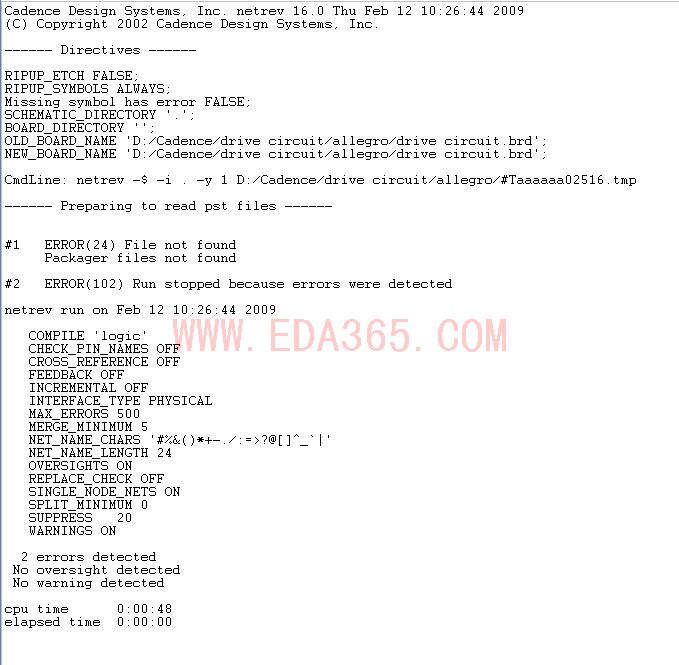

不管错误继续导入网络表出现信息如下:

把netlist.log传上来看看呢,你贴的图片上看不出有用的信息

元件的PCB Footprint属性都添加了么?

张伊园同学

小编不关注阿,问了问题就跑

3# 袁荣盛 呵呵,都添加了的呀,DRC检查时都没错也,但是就是生成网络表时就不行了,

直接确定,随后出现Allegro界面,然后导入网络表,

出现这个文件后就不能导入原件了。

原理图中的封装信息都添加了的。

传上来看下

6# dingtianlidi 什么传上来看一下呀,呵呵,我都传上来了呀。

不要把Capture导出网表和Allegro导入网表放在一起做

分开一步一步做

然后再检查确认哪一步出了问题

capture导出网表前确认所有器件的PCB Footprint都已设置了值

8# 袁荣盛

看到一个熟人,哈哈。

上面的错误好像是说没有封装,

你是第一方直接生成的吧? 在目录下看下netlist.log看下

你用第三方可以试下~

11# superlish

我不知道你说的第三方生成是什么意思,我说一下我做这一段的步骤吧:

1、首先绘制原理图,这里有几个元件是自己画的因为库里面没有,然后画了相应的封装,并且把所有元件与其封装对应起来(对元件设置的相应的值)。

2、DRC检查,选择page1,点击![]()

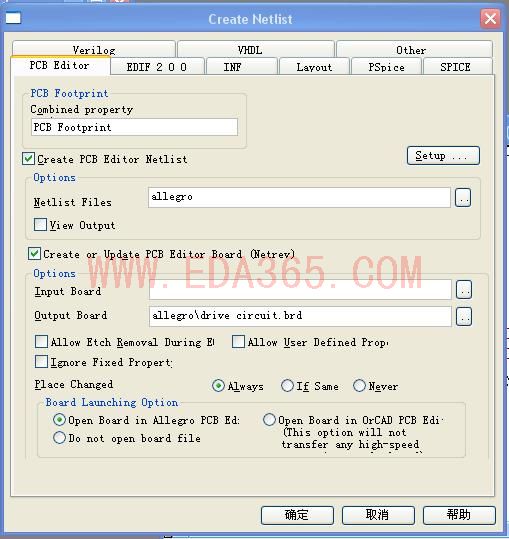

3、生成网络表,在相同页面下,点击

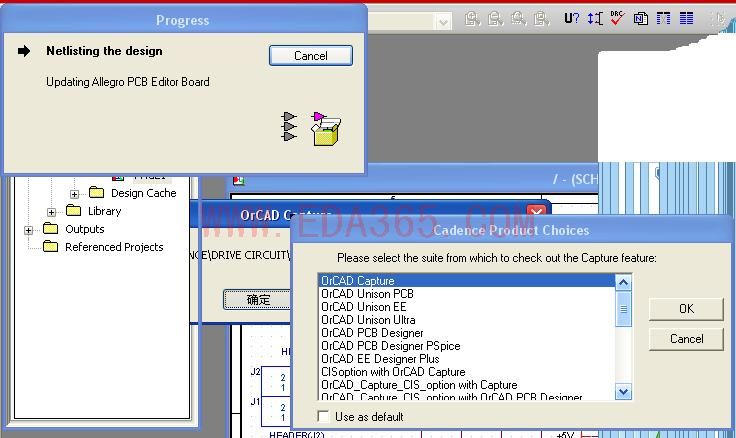

点击确定,----->

点击确定,-----> 确定---->

确定----> OK---->

OK---->

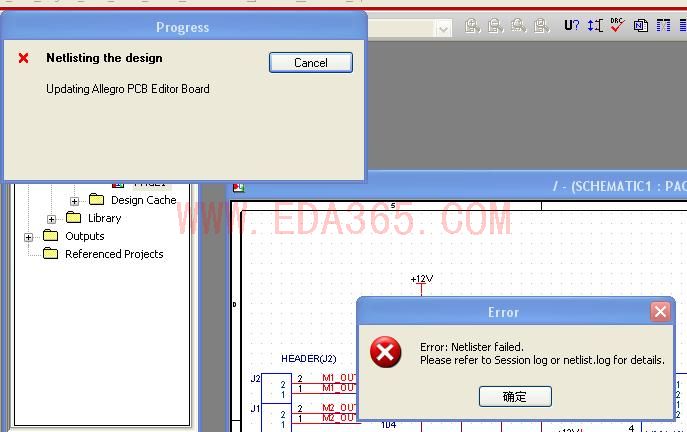

这是生成网络表时出现的问题,大家帮忙看看到底是怎么回事吧。

导出网表时不要选中creat or update...

然后打开Allegro,file--import logic

选择cis 下面网表路径要对应你Capture CIS生成网表时的那个路径就OK了

13# 袁荣盛

师傅!按照你说的做了,但是还是出现了这个

不能成功导入网络表,是怎么回事呀?!

Allegro的design path中的路径要设置正确

pad path设置为你pad放置的路径

psm path设置为你psm ssm fsm 等等*sm放置的路径,有几个路径设置几个路径

Allegro查找的时候从上往下查找的,最上面的优先级别最高

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:请问,OrCAD中能把元件封装做成这个效果吗?

下一篇:ORCAD16.2输出的网表在PADS2007中导入 会有BUG吗