- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

orcad 仿真

录入:edatop.com 点击:

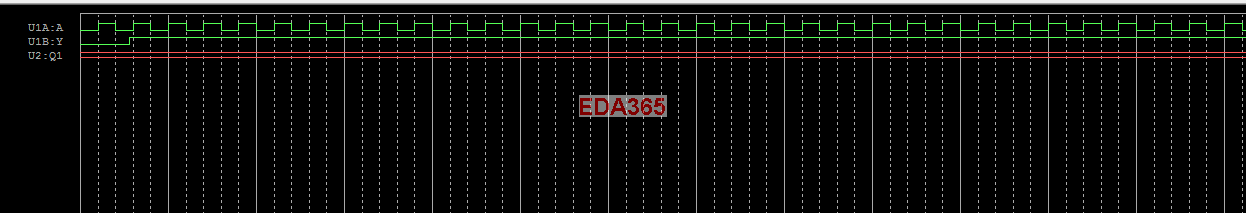

最近在放一个简单的PLL电路,发现分频器CD4040B不能正常工作,输出的总是两道红杠,期望有人给指点一下。

4040的model

*-------------------------------------------------------------------------

* CD4040B CMOS Ripple-Carry Binary Counter/Dividers

*

* The CMOS Intergrated Circuits Databook, 1983, RCA Solid State

* atl 10/3/89 Update interface and model names

*

.subckt CD4040B INPUT RESET Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11 Q12

+ optional: VDD=$G_CD4000_VDD VSS=$G_CD4000_VSS

+ params: MNTYMXDLY=0 IO_LEVEL=0

UBUF buf VDD VSS

+ INPUT IN

+ D0_GATE IO_4000B_ST IO_LEVEL={IO_LEVEL}

UCLRB inv VDD VSS

+ RESET CLRB

+ D0_GATE IO_4000B IO_LEVEL={IO_LEVEL}

UT anda(2,10) VDD VSS

+ Q1ID Q2I

+ T3 Q3I

+ T4 Q4I

+ T5 Q5I

+ T6 Q6I

+ T7 Q7I

+ T8 Q8I

+ T9 Q9I

+ T10 Q10I

+ T11 Q11I

+ T3 T4 T5 T6 T7

+ T8 T9 T10 T11 T12

+ D_CD4040B_1 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ1ID buf VDD VSS

+ Q1I Q1ID

+ D_CD4040B_1 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ1I jkff(1) VDD VSS

+ $D_HI CLRB IN $D_HI $D_HI Q1I $D_NC

+ D_CD4040B_2 IO_4000B MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

UQ2I jkff(1) VDD VSS

+ $D_HI CLRB Q1ID $D_HI $D_HI Q2I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ3I jkff(1) VDD VSS

+ $D_HI CLRB T3 $D_HI $D_HI Q3I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ4I jkff(1) VDD VSS

+ $D_HI CLRB T4 $D_HI $D_HI Q4I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ5I jkff(1) VDD VSS

+ $D_HI CLRB T5 $D_HI $D_HI Q5I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ6I jkff(1) VDD VSS

+ $D_HI CLRB T6 $D_HI $D_HI Q6I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ7I jkff(1) VDD VSS

+ $D_HI CLRB T7 $D_HI $D_HI Q7I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ8I jkff(1) VDD VSS

+ $D_HI CLRB T8 $D_HI $D_HI Q8I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ9I jkff(1) VDD VSS

+ $D_HI CLRB T9 $D_HI $D_HI Q9I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ10I jkff(1) VDD VSS

+ $D_HI CLRB T10 $D_HI $D_HI Q10I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ11I jkff(1) VDD VSS

+ $D_HI CLRB T11 $D_HI $D_HI Q11I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ12I jkff(1) VDD VSS

+ $D_HI CLRB T12 $D_HI $D_HI Q12I $D_NC

+ D_CD4040B_3 IO_4000B MNTYMXDLY={MNTYMXDLY}

UQ1 jkff(1) VDD VSS

+ $D_HI CLRB IN $D_HI $D_HI Q1 $D_NC

+ D_CD4040B_4 IO_4000B MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

UQ bufa(11) VDD VSS

+ Q2I Q3I Q4I Q5I Q6I Q7I Q8I Q9I Q10I

+ Q11I Q12I

+ Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10

+ Q11 Q12

+ D_CD4040B_1 IO_4000B MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

另外一个问题就是,像这种内部变量的值,在那边设置呢

+ optional: VDD=$G_CD4000_VDD VSS=$G_CD4000_VSS

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:制作Title Block时,怎么插入属性的文本?就是以后调用时可以更改的那部分?

下一篇:cis 自动备份的方法