- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

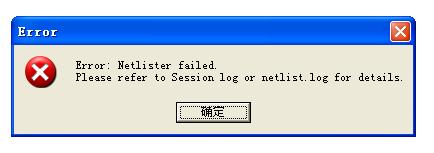

导入ALLGERO出错,请CAPTURE资深工程师指教

红字的那个错误是哪里出的问题,我一直找不到问题的所在

--------------------------------------------------------------------------------------------------------------------------------------The following 1 points have been identified as net connectivity change points from the last operation--------------------------------------------------------------------------------------------------------------------------------------(66.04, 109.22)--------------------------------------------------------------------------------------------------------------------------------------The following 1 points have been identified as net connectivity change points from the last operation--------------------------------------------------------------------------------------------------------------------------------------(55.88, 109.22)********************************************************************************** Netlisting the design *********************************************************************************Design Name:D:\Cadence\Design\SCH\yq.dsnNetlist Directory:D:\Cadence\Design\SCH\allegroConfiguration File:C:\Cadence\PSD_15.0\tools\capture\allegro.cfg

Spawning... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"Scanning netlist files ...Loading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstxprt.datLoading... D:\Cadence\Design\SCH\allegro/pstxnet.datError: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Reference designators inconsistent in xprt and xnet files Detected in function: pstFindInstByOldPathName Error: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Error loading the net list file Detected in function: ddbLoadPstXFiles #1 Error [ALG0036] Unable to read logical netlist data.

Exiting... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"

*** Done ***

********************************************************************************** Spawing Allegro *********************************************************************************Spawing "C:\Cadence\PSD_15.0\tools\pcb\bin\allegro.exe" -mpssession LYZA "D:\Cadence\Design\SCH\allegro\yq.brd"

*** Done ***

********************************************************************************** Netlisting the design *********************************************************************************Design Name:D:\Cadence\Design\SCH\yq.dsnNetlist Directory:D:\Cadence\Design\SCH\allegroConfiguration File:C:\Cadence\PSD_15.0\tools\capture\allegro.cfg

Spawning... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"Scanning netlist files ...Loading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstxprt.datLoading... D:\Cadence\Design\SCH\allegro/pstxnet.datError: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Reference designators inconsistent in xprt and xnet files Detected in function: pstFindInstByOldPathName Error: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Error loading the net list file Detected in function: ddbLoadPstXFiles #1 Error [ALG0036] Unable to read logical netlist data.

Exiting... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"

*** Done ***

********************************************************************************** Spawing Allegro *********************************************************************************Spawing "C:\Cadence\PSD_15.0\tools\pcb\bin\allegro.exe" -mpssession LYZA "D:\Cadence\Design\SCH\allegro\yq.brd"

*** Done ***

********************************************************************************** Netlisting the design *********************************************************************************Design Name:D:\Cadence\Design\SCH\yq.dsnNetlist Directory:D:\Cadence\Design\SCH\allegroConfiguration File:C:\Cadence\PSD_15.0\tools\capture\allegro.cfg

Spawning... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"Scanning netlist files ...Loading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstxprt.datLoading... D:\Cadence\Design\SCH\allegro/pstxnet.datError: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Reference designators inconsistent in xprt and xnet files Detected in function: pstFindInstByOldPathName Error: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Error loading the net list file Detected in function: ddbLoadPstXFiles #1 Error [ALG0036] Unable to read logical netlist data.

Exiting... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"

*** Done ***

********************************************************************************** Spawing Allegro *********************************************************************************Spawing "C:\Cadence\PSD_15.0\tools\pcb\bin\allegro.exe" -mpssession LYZA "D:\Cadence\Design\SCH\allegro\yq.brd"

*** Done ***

********************************************************************************** Netlisting the design *********************************************************************************Design Name:D:\Cadence\Design\SCH\yq.dsnNetlist Directory:D:\Cadence\Design\SCH\allegroConfiguration File:C:\Cadence\PSD_15.0\tools\capture\allegro.cfg

Spawning... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"Scanning netlist files ...Loading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstchip.datLoading... D:\Cadence\Design\SCH\allegro/pstxprt.datLoading... D:\Cadence\Design\SCH\allegro/pstxnet.datError: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Reference designators inconsistent in xprt and xnet files Detected in function: pstFindInstByOldPathName Error: Line 1875 in file D:\Cadence\Design\SCH\allegro/pstxnet.dat: Error loading the net list file Detected in function: ddbLoadPstXFiles #1 Error [ALG0036] Unable to read logical netlist data.

Exiting... "C:\Cadence\PSD_15.0\tools\capture\pstswp.exe" -pst -d "D:\Cadence\Design\SCH\yq.dsn" -n "D:\Cadence\Design\SCH\allegro" -c "C:\Cadence\PSD_15.0\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"

*** Done ***

ERROR [CAP0028] Unable to find object.ERROR [CAP0028] Unable to find object.ERROR [CAP0028] Unable to find object.

********************************************************************************** Design Rules Check*********************************************************************************

Checking Pins and Pin ConnectionsERROR [DRC0036] Wire crosses pin but is not connected U8,A48: SCHEMATIC1, CPU (7.10, 5.50)

--------------------------------------------------Checking Schematic: SCHEMATIC1--------------------------------------------------Checking Electrical Rules

Checking for Unconnected NetsWARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source SEG[00:17]: SCHEMATIC1, CPU (2.60, 3.40) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0007] Net has no driving source C[00:15]: SCHEMATIC1, CPU (0.30, 4.90) WARNING [DRC0006] Net has fewer than two connections SEG0: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG1: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG2: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG3: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG4: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG5: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG6: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG7: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG8: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections SEG9: SCHEMATIC1, CPU (0.30, 4.70) WARNING [DRC0006] Net has fewer than two connections C0: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C1: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C2: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C3: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C4: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C5: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C6: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C7: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C8: SCHEMATIC1, CPU (7.10, 3.90) WARNING [DRC0006] Net has fewer than two connections C9: SCHEMATIC1, CPU (7.10, 3.90)

Checking for Invalid References

Checking for Duplicate References

Check Bus width mismatch

*********************************************************************************

说得很清楚了: 封装和原理图符号的管脚定义不一致.

Symbol 'TQFP100' for device 'EM78811_TQFP100_EM78811' has extra pin '30'.

除了封装和part的不一致外,好像还有别的原因

以下是引用phoenixbb在2004-9-2 21:13:23的发言:除了封装和part的不一致外,好像还有别的原因