- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

ALLEGRO覆铜的问题

录入:edatop.com 点击:

大家好,请教大家,ALLEGRO覆铜的时候,铜皮和焊盘之间的那一圈间距是怎么确定的呢?一般设置的焊盘有TOP层,还有SOLDERMASK层,这个铜皮和焊盘之间的间距是依照TOP层来确定铜皮和焊盘之间的间距呢,还是按照SOLDERMASK层呢,

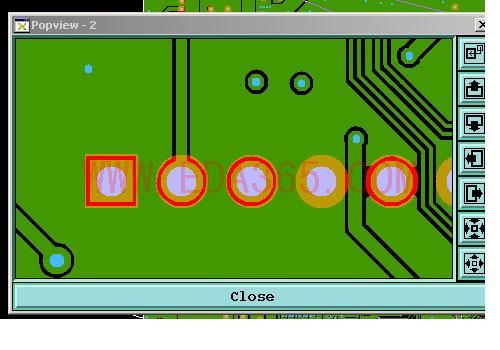

此图是板厂回复的信息的一个图,说文件中有器件孔的阻焊开窗太大,盖到相邻的铜皮上,就是SOLDERMASK层做的有一点大,可是大家看这个图

此图是板厂回复的信息的一个图,说文件中有器件孔的阻焊开窗太大,盖到相邻的铜皮上,就是SOLDERMASK层做的有一点大,可是大家看这个图

是MARK点,周围很大一块是没有铜皮的区域是SOLDERMASK,这块却避开了铜皮,为什么再做直插焊盘的时候覆铜却没有避开SOLDERMASK的最外围呢,覆铜的避开区域这块到底是按照TOP层来定呢,还是按照SOLDERMASK层呢,有一点弄不明白了

是MARK点,周围很大一块是没有铜皮的区域是SOLDERMASK,这块却避开了铜皮,为什么再做直插焊盘的时候覆铜却没有避开SOLDERMASK的最外围呢,覆铜的避开区域这块到底是按照TOP层来定呢,还是按照SOLDERMASK层呢,有一点弄不明白了

觉得是按照TOP层来避开了,按照SOLDERMASK避开是没有道理

都不是,MARK点是建了route keepout区域,所以铜皮避开.

恩,的确,封装中的确这么定义的,那看来我的SOLDERMASK层是不能定义太大,是把

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:问一下:allegro15.5 和pads哪一个更好用一点

下一篇:Symbol 。 must be "dbdoctor"ed