- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro常用属性积累

如,Fixed, 使元件不能被移动

说的很好,可以开一个专帖来讨论这类问题。想法不错,支持!

恩·谁能做个PDF

还是讨论比较好一些,最后再汇总。

先来一个SHAPE的

OK_UNASSIGNED_SHAPE

定义该属性的SHAPE如果没有NET属性,不会被列为Unassigned Shapes。

呃,小编的那个在我的allegro里面咋没看见啊

no_rats 可以使飞线不显示。 F12 选择某net再选no_rats

觉得这个提议不错

VOLTAGE,RATSNEST_SCHEDULE

改变鼠线连接方式

voltage属性主要是为了用于后面si仿真,要不然电源网络会被当做普通网络,导致产生许多xnet,出现仿真错误,如果没有设置,进行仿真前在Setup Advisor中会要求指定该属性(设置DC电压值),如果不仿真可以不用设;

如果给某个网络添加了voltage属性,则默认该网络的显示属性为norat属性,显示方式为框x

如果想改变显示模式可以添加RATSNEST_SCHEDULE中选定属性

一眨眼 两个多月过去了 再次看到这个帖子

我们不仿真,不用考虑仿真的问题。

我之所以习惯用voltage,只是因为它是列表里倒数第五个,比较好找……

直接把滚动条拉到底就看到它

再来一个:

PACKAGE_HEIGHT_MAX 、 PACKAGE_HEIGHT_MIN

改变器件高度信息,消除因PLACE_BOUND 重叠而引起的DRC

方法比较山寨,慎用!

rt:

comps的:SIGNAL_MODEL

虽然不仿真,但这样加Xnet确实很方便!比在Analyze→si/emi sim→model……设要方便得多

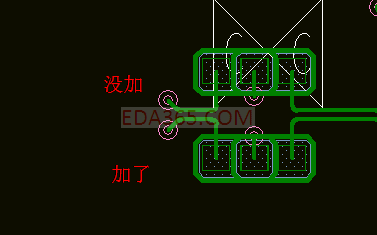

给VIA添加NO_SHAPE_CONNECT属性,则VIA只可以与CLINE相连,跟SHAPE会自动避开。

我知道的大家可能都知道,所以没什么好说的。倒是想问一个:

NET: Route_Priority

这个是起什么作用的?