- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

求助:SDRAM等长线设置问题

录入:edatop.com 点击:

小弟最近要画SDRAM的板子,前面看了关于XNET设置等长的帖子,然后根据帖子说的已经照做了,在设置约束规则的窗口里已经将所有的数据线D0-D31XNET的pin pair都设置好,而且组成了SDRAM_DATA的group;在Delta: Tolerance设置成:0 MIL : 150 MIL了,如下图所示:

图1 XNET的规则设置

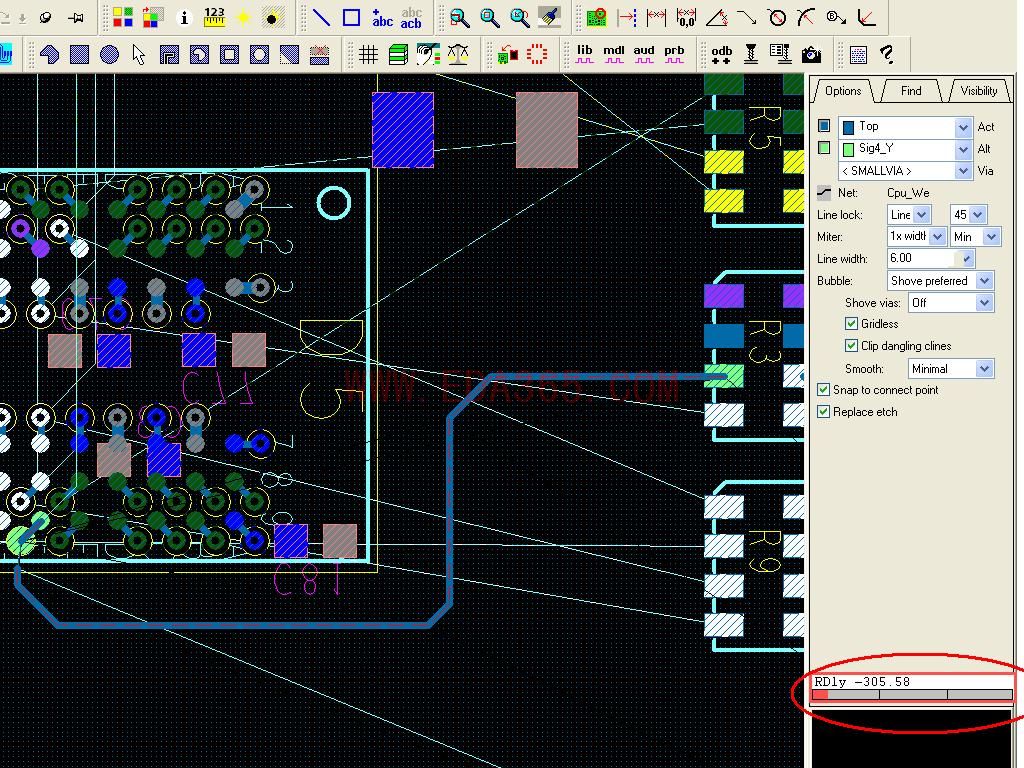

可是,设置好后在allegro中画线时遇到了问题,就是在经过我串联的22欧排阻时(XNET已经设置好),Rdly要么是黄色,要么是红色,就是到不了绿色,如下图:

图2 Rdly黄色

图3 Rdly红色

请问这个黄色和红色是怎么回事呢?是提示我什么错误啊?

我的想法是将D0-D31这些线都设置成长度为2000mils的数据线,且等长范围在0-150mil以内(线长在1925mils-2075mils),请问要达到这个要求还需要在哪里进行设置啊?

有知道的请帮忙解答一下,谢谢!

CPU与2片SDRAM相连

我的CPU的地址线A3(A点)通过过孔VIA(B点)连接到SDRAM1的A3管脚(C点)和SDRAM2的A3管脚(D点),所以这3个管脚的网络标号都是CPU_A3;

我想要达到AC=AD的目的,且AC和AD的长度都在(1925, 2075)范围内,而Total Etch Length长度是指:

Total Etch Length = AB + BC + BD;

所以我觉得无法通过设置Total Etch Length的MIN/MAX来实现等长;

不止CPU的A3这一根线,CPU所有的地址线都是这样的,既要连接到2片SDRAM,又要相对等长;

有没有画过SDRAM或者DDR的高人啊?指点一下吧

小弟先谢过!

图1 XNET的规则设置

可是,设置好后在allegro中画线时遇到了问题,就是在经过我串联的22欧排阻时(XNET已经设置好),Rdly要么是黄色,要么是红色,就是到不了绿色,如下图:

图2 Rdly黄色

图3 Rdly红色

请问这个黄色和红色是怎么回事呢?是提示我什么错误啊?

我的想法是将D0-D31这些线都设置成长度为2000mils的数据线,且等长范围在0-150mil以内(线长在1925mils-2075mils),请问要达到这个要求还需要在哪里进行设置啊?

有知道的请帮忙解答一下,谢谢!

还没有设置参考线吧

楼上的能不能再说得 详细一点

在哪里设?或者如何设啊?

(线长在1925mils-2075mils),直接在Total Ecth Length 设一下MIN MAX...就行了,搞那么麻烦。

那total etch length和propagation delay有什么区别啊?

shuy7love7:

我按照你说的试了一下,觉得不行;

我的PCB是这样的:

CPU与2片SDRAM相连

我的CPU的地址线A3(A点)通过过孔VIA(B点)连接到SDRAM1的A3管脚(C点)和SDRAM2的A3管脚(D点),所以这3个管脚的网络标号都是CPU_A3;

我想要达到AC=AD的目的,且AC和AD的长度都在(1925, 2075)范围内,而Total Etch Length长度是指:

Total Etch Length = AB + BC + BD;

所以我觉得无法通过设置Total Etch Length的MIN/MAX来实现等长;

不止CPU的A3这一根线,CPU所有的地址线都是这样的,既要连接到2片SDRAM,又要相对等长;

有没有画过SDRAM或者DDR的高人啊?指点一下吧

小弟先谢过!

我上次也是1拖2,大概步骤是这样

1,将cpu pin的属性设为out,将sdram pin的属性设为in;

2,在constraint里,设min/max propagation delay,选pin pairs是all drivers to all receivers,

你就可以实现cpu分别到sdram都是等长。

感谢chenxztiger,你说的方法可行

另外我还想问一下,那个Relative Propagation Delay是干嘛用的?设置了这个有什么用?

DDR的等长标准设置是怎么样的?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro 中要显示Value 如何做

下一篇:Cadence Product Choices选择框的内容少了