- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

寻找Design Entry HDL高手看下我的问题

录入:edatop.com 点击:

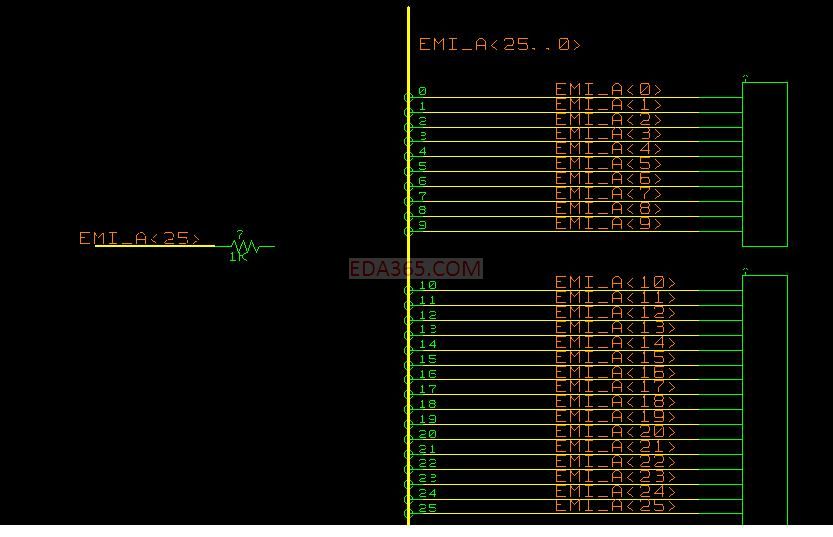

我有一个总线命名为 EMI_A<26..0>, 而同一层次(即同一页原理图)有一个信号要用EMI_A25,那么我给这个信号命名为EMI_A25的时候,这个信号跟总线上的EMI_A25实际上不连在一起的,看一下总线上的这个网络名显示为EMI_A<25>,但是如果我把这个单独的网络命名为EMI_A<25>,软件又是不允许使用<>的,保存的时候会报错。如果涉及的页间的网络连接,也会因此出一些问题。

而在其他的设计工具中,一般情况是总线命名为EMI_A<26..0>,那么各个信号线的网络名实际是EMI_A26/25....

这个软件到底是什么规则呢?望高手指教。

我昨天把网络命名为EMI_A<0>/<1>/<2>...后(就是你发的图中那样),保存的时候总提示有错误(忘记下来什么错误了),我就以为网络名里面不能带<>,所以我想了另一种方法,见附图。可是今天我又把网络名命名为EMI_A<0>/<1>/...后,保存时没问题的!

不知道用我的附图中的这种方式是不是有什么问题?

而在其他的设计工具中,一般情况是总线命名为EMI_A<26..0>,那么各个信号线的网络名实际是EMI_A26/25....

这个软件到底是什么规则呢?望高手指教。

把网络名复制过去就可以了。

我昨天把网络命名为EMI_A<0>/<1>/<2>...后(就是你发的图中那样),保存的时候总提示有错误(忘记下来什么错误了),我就以为网络名里面不能带<>,所以我想了另一种方法,见附图。可是今天我又把网络名命名为EMI_A<0>/<1>/...后,保存时没问题的!

不知道用我的附图中的这种方式是不是有什么问题?

你的网络名是你一个一个加上去的? 还是用wire--bus name 加上去的?

是我一个一个加上去的。

从导到PCB的网络连接关系看,这样好像也是没问题的。

不知道会有什么潜在的问题吗?

这样也太费力了,到PCB中不会有问题。其实这个网络名都不用加的,你定义了总线的名称,做了bus tap value就可以了。

是这样的,如果只是总线的连接,那做了bus tap value就可以了。

但是我现在总线中的其中一个信号线又要做其他的复用,而我之前用powerlogic机ORCAD的时候,给总线命名为EMI_A[26..0]的时候,每个网络的名字是EMI_A0/....,这样我要复用其中的任何一个网络的时候,都是直接命名网络为EMI_A0/...。

而在Design Entry HDL中,如果我起了总线名EMI_A[26..0],复用的网络我又命名为EMI_A0/...的时候,实际上是没有连接在一起的。

所以,就出了问题。

然后,我把EMI_A0改成了EMI_A<0>,保存的时候却提示错误!不知道什么问题,我就按照我以上较费力的方法改了下就OK了!但是我后来又把EMI_A<0>后保存,却又没有错误提示了!

刚开始用这个软件,不是很熟

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:怎样在约束管理器ECsets中创建pin-pair,小白问题请教

下一篇:跪求:可以将‘零件和cline 及via 同时mirror的skill或者其他方法