- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DDR等长,谁更长?

1、是时钟线长海是要求数据线更长呢?

2、我现在是数据线等长,地址线和控制线等长,等长的范围是20mile 内误差,不知道是否可以呢?

我这有DD2和ARM9核的板,官方给出的建议是:

时钟CK,CK#:600-1400MILS

地址和控制信号:CK+200MIL

数据信号:CK+/-125MIL

数据信号DQ[0..7], DM0 = +50mils of DQS0.DQ[8..15], DM1 = +50mils of DQS1

我在实际layout的时候也按照这个做,信号组内误差+-20MIL,没出什么问题

问下,这些信息是从哪看看到。给个具体地址吧。一直找不到。

谢谢。

同样疑问:

三星3SC6410的Circuit Design Guide中描述:

These clock signals must have differential impedance. The length of clock signal is longer than signals in data signal group and control signal groups.

{DQ, DQM, DQS} < {CSn, CKE, ADDR, BA, RASn, CASn, WEn, AP} < {SCLK, SCLKn}

要看design guide

1、时钟线长

2、你的等长可以,但是还要控制数据和地址等长,起码不要差的太多。

因为一般是:

地址比数据长

地址和CK+/-等长 范围100mil左右

DQS和CK+/-等长 范围可稍放宽些

DQS和同组数据等长 误差尽量小,控制在1mm内最好

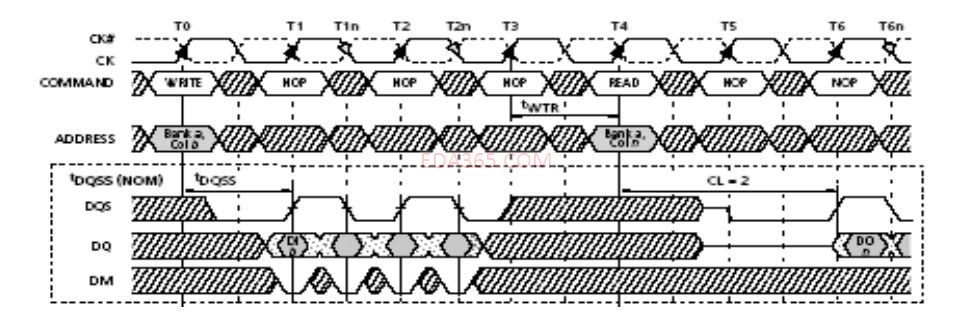

大家请看这个图片呢!我觉得应该是CLK最长吧!

重要的是要讲理由,我觉得不能乱说,请大家指点!

大家给点意见啊!

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:Cadence高速电路板设计与仿真(第3版)资源下载

下一篇:请问作为cache的sram,数据线在layout的时候可以交换吗?地址线呢