- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

再发Constraint Manager疑难杂症,高手请进!

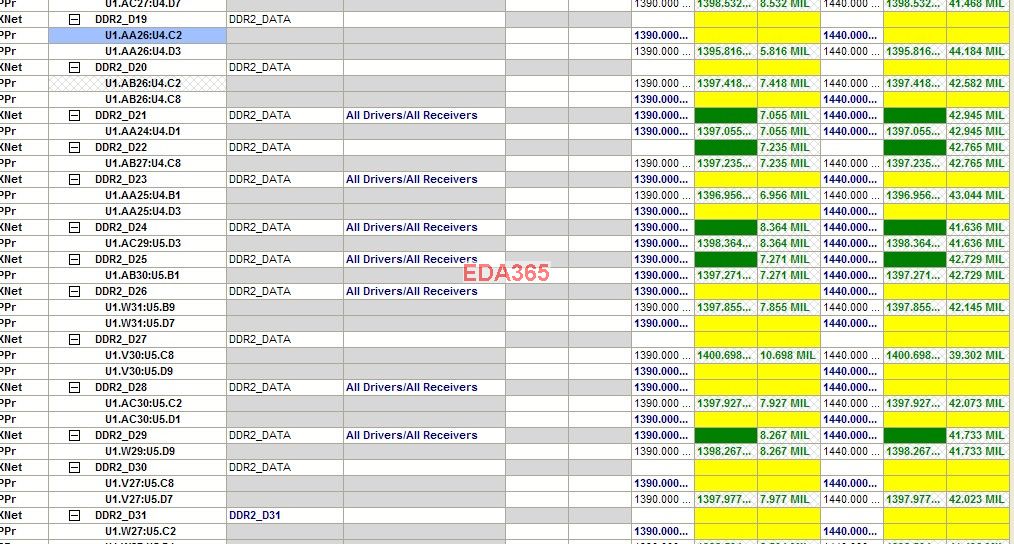

如图中所示,数据线都是一对一的,凭空跑出来很多没用的线,黄色所示,都是其他引脚已经连接的。检查原理图没有问题,没用这些连接关系都是一对一的。

前两天发帖有朋友说是模型问题,我用的是排阻,4个一起的。模型都用的一样的,总共64条线别的都没问题,单单这几个有问题,请教高手有遇到过这种情况的吗,该如何解决。先谢了

是的,需要重设模型!

你确定一对一?

pin pair改longest或者手动设pin pair试试~

pin pair下清空 scope选择global

关于pin pair下的选项help里面的说明是

Match Group. In the Pin Pairs column of the Relative Propagation Delay worksheet, you can guide the generation of pin pairs with the following options:

Choosing this option . . .

Generates pin pairs based on . . .

All Drivers/All Receivers

All combinations of drivers and receivers.

Longest Driver/Receiver

The longest driver-receiver pin pair. Uses the longest pin pair when there are not any drivers or receivers.

Longest Pin Pair

The longest pin pair.

建模的时候pin number 12345678对应错了是不是?

回复 wangjing 的帖子

没错啊 对应关系也对着呢 一样的模型 有的是对的 有的是错的

回复 wangxs_song 的帖子

模型都没问题啊

回复 mcu200689 的帖子

你的排阻是不是上拉或下拉?就是一端是电源或者地?而并非两端都是信号。

今天找到问题的所在了,DDR2组内8跟数据线是可以互换的,为了布线方便就把原来的一组内的8跟数据线做了调换,约束里边的两条线是换前和换后的(一条绿的是现在的连接关系,黄的是原来的),应该是生成网表的的时候,新的连接关系没有替换掉原来的,造成两根线同时共存,这种情况应该就是OrCad画原理图时的问题了,不知道这种情况怎么解决?

回复 mcu200689 的帖子

调整原理图再导网表啊

回复 wangjing 的帖子

怎么调?原理图连接关系对着呢啊

回复 mcu200689 的帖子

对着呢怎么会这样,重导网表。

回复 wangjing 的帖子

导啦 我改了连接关系就重新生成网表 导到PCB了 约束关系还是显示两条线 不知道咋回事

回复 mcu200689 的帖子

不应该会这样 你的原理图没改好吧 再检查一下。换个路径再导一下

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:怎么把spb16.5 Allegro Design Entry的start Page禁止掉?

下一篇:SPB 16.5 的試用 : PSPICE 功能未全部打開