- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教为什么要这样调整网络的拓扑结构。周润景《cadence高速电路板设计与仿真》书上的

录入:edatop.com 点击:

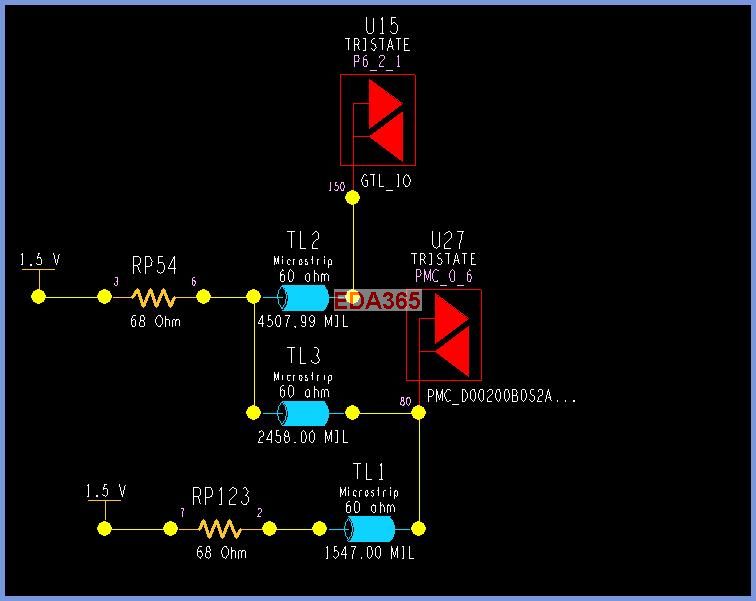

书中P526,先是提取HA3的拓扑结构如下

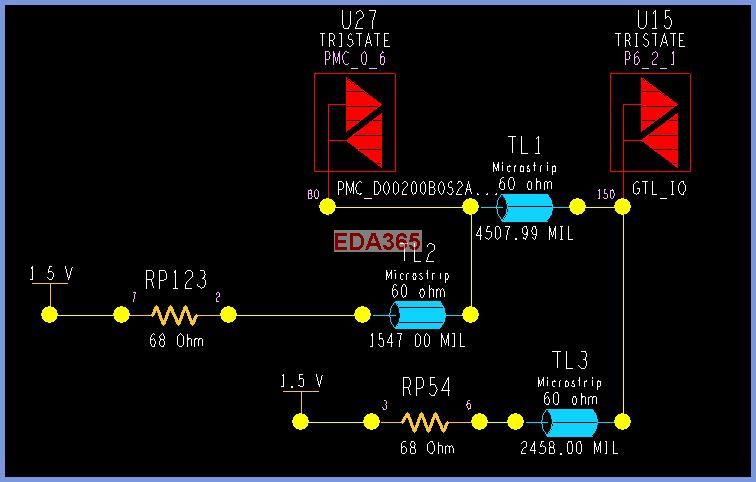

然后修改成这样:

为什么要作这样的调整?书上的这个例子是PC主板的GTL 66MHz Host总线的一部分。

第一张图可能不太清楚,点击一下再放大就能看清楚了。请大家帮忙看看,这里面究竟是什么道理。

我再顶!顶顶顶!

尽信书不如无书,个人觉得周润景的书看看还行,较真就没必要了,他貌似只是老师,没有什么实战经验吧,看他出的书,从protel,altium,multisim,cadence,mentor wg....还有FPGA之类的,几乎囊括了所有常见EDA软件了,一个人有这么多精力出书,那水平能高到哪去

有时还是要结合实际去看问题

你看一个调整后的三段线的长度就明白了。

一般上拉都应该是靠近输出、输入端的,不应该是在半中间的

回复WJL882008:我看不懂你的话,能够结合具体说一下吗?你说的上拉电阻是指?

有道理!

请问楼上,你看得出其中有什么道理么?

还没看到那部分呢

你也在看这本书啊。

再顶!我顶!我顶!我顶顶顶!

呵呵,他写的书只是告诉你如何使用,但他应该没有什么高频的实际经验,只要知道一种方法,至于具体的高频设计方面你还是看其它书或是自已慢慢的摸索吧!

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro 16.3 哪里可以看到补丁安装成功的

下一篇:关于用desig entry hdl 编辑part库时格点设置问题