- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请教一个八层板的叠层问题

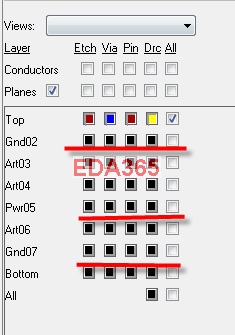

我现在的层叠结构是

TOP

POWER1

S1

GND

S2

S3

POWER2

BOTTOM我的TOP层和BOTTOM层板子的最下面位置有差分的SATA信号,由于元件非常多TOP层和BOTTOM层基本上没有走线,我同事说这样的叠层电源完整性有问题,建议把S2和POWER2和到一层,增加一层地

如下层叠

TOP

GND

POWER

S1

S2

S3

GND

BOTTOM

但是这样的话S2就没有参考平面了,大家给我个建议啊用哪种?谢谢!

你这样信号就好么?

必须三个走线层?而且你现在叠层也不对称

电源搁一层吧。

top,gnd,s1,vcc,gnd,s2,gnd,bottom

按top,pow1,s1,S2,gnd,s3,pow2,bottom ,我可以帮你核算一份阻抗设计及层叠结构给你.

我现在板子上只能三个走线层才能走通,所以没办法做到3个GND层,纠结啊

电源也非常多,我现在是在电源层和S2层走的电源

帮忙推荐一下阻抗控制和层叠结构啊,单端50ohm,top、bottom层有SATA差分线,差分100ohm,

谢谢了!

可以的,不用谢1!

lZ的叠层急不合理,要么按三楼的要么加层。

top,gnd,ss, pwr,pwr,ss,gnd,bottom

这个是我们比较常见的!

板子的尺寸比较小元件放置的很慢,所以TOP BOTTOM层上基本不能走线,所以中间要3个信号层才能走出来,

纠结啊,帮忙看看有没有什么好的办法啊?

三楼的叠层不错,但是满足不了你3层信号的要求,可是你用三层信号,叠层不对称嘞,这个叠层怎么样?不过走线时需要特别注意。

top-S1-GND-S2-S3-POWER-S4-BOTTOM

top基本没有走线,S1不用担心有长距离的平行线,S1和S2不用担心跨分割,而S3和S4走线要小心跨分割,同时S3小心与S2长距离平行线。

50欧姆阻抗控制:S1/S4 6.5mil

S2/S3 7mil

100欧姆阻抗控制:S1/S4 线宽5mil 线间距8.5mil

S2/S3 5mil 8mil

重要信号走在06层

04层可以铺铜处理部分电源,但是注意第3层有走线的地方,对应04层不要铺大块铜,不然会改变阻抗参考层!

通常典型的分层同意3楼的,不过楼上的叠层很好,满足lz要求。 支持

12楼的不错,我马上要设计的电路板就这样的。

12楼的叠层我用到过,

是在4片DDR2 正反对贴,64位两个内层布线很困难,所以添加一个信号层。这样DDR2的数据线同组同层容易多了!