- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

求助阻抗结构设计的阻抗计算方法

录入:edatop.com 点击:

各位前辈,最近要做一个100ohm阻抗匹配的差分信号的基板。

按照坛子里大虾的方法用si9000计算了一下。发给pcb厂商确认。基板厂商回复如下:

建议差分线改为5.5/5.5mil,叠层更改如下:

———————————— top 18um

5.6mil PP ER 4.2

|———————————| L2/L3 35/35um

| 47.25mil | ER 4.7

|———————————|

5.6mil PP ER 4.2

———————————— bot 18um

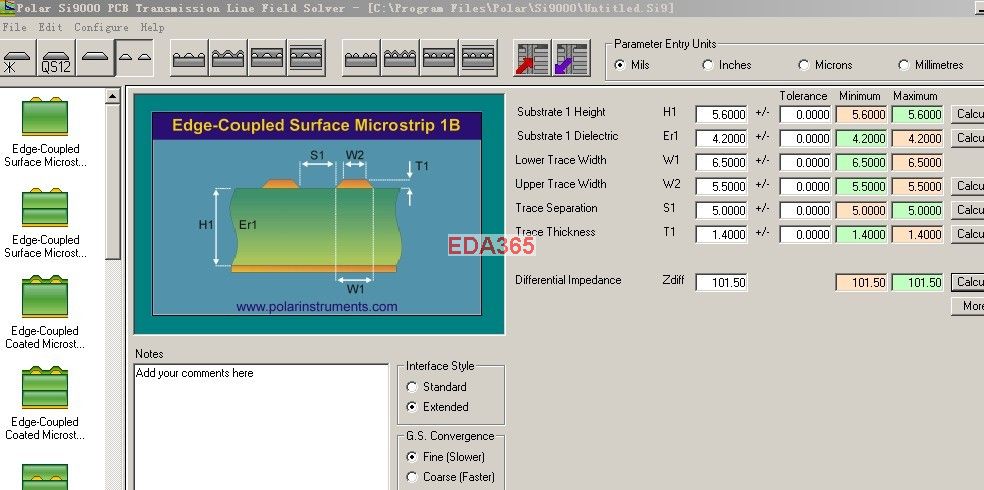

我用si9000计算了一下:

H1=5.6

Er1=4.2

W1=6

W2=5

S1=5.5

T1=0.7(18um=0.7mil)

计算出来Zdiff=112.99,是不是不符合要求了呢?如果不符合要求的话为什么基板厂商会这么推荐呢?

谢谢大家了。

按照坛子里大虾的方法用si9000计算了一下。发给pcb厂商确认。基板厂商回复如下:

建议差分线改为5.5/5.5mil,叠层更改如下:

———————————— top 18um

5.6mil PP ER 4.2

|———————————| L2/L3 35/35um

| 47.25mil | ER 4.7

|———————————|

5.6mil PP ER 4.2

———————————— bot 18um

我用si9000计算了一下:

H1=5.6

Er1=4.2

W1=6

W2=5

S1=5.5

T1=0.7(18um=0.7mil)

计算出来Zdiff=112.99,是不是不符合要求了呢?如果不符合要求的话为什么基板厂商会这么推荐呢?

谢谢大家了。

自己顶一下。

T1错了啊,T1是指成品铜厚,应该是1.4MIL.

最好稍修改一下线宽如下图:

阻抗图1

非常感谢,第一次考虑阻抗问题。

弱弱的问一句,成品铜厚1.4mil是怎么算出来的呢?

谢谢。

回复 liuyian2011 的帖子

也没说成品铜厚要多少呀?

按小编给的数值的,他算出来的阻抗值确实是这样。

一般制板厂商电镀工序,通常会使铜加厚0.5OZ,也就是说:如采用0.5OZ的基铜,成品铜厚就是1OZ,

如采用1OZ的基铜,成品铜厚就是1.5OZ,如采用2OZ的基铜,成品铜厚就是2.5OZ,如采用3OZ的基铜,成品铜厚就是3.5OZ。 如果客户要求成品2OZ,制板厂商会采用1OZ基铜,通过电镀到1.5OZ,再进行加镀到2OZ.

也就说在计算阻抗的时候,铜厚要按成品的厚度计算?

YES

回复 liuyian2011 的帖子

谢谢!

懂了,谢谢指点。

牵涉到工艺问题,事情就复杂了。不懂工艺是做不好设计的。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:问个关于ALLEGRO补丁的问题?

下一篇:allegro画板时遇到的问题