- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

8层板,这样的参数阻抗控制如何实现?

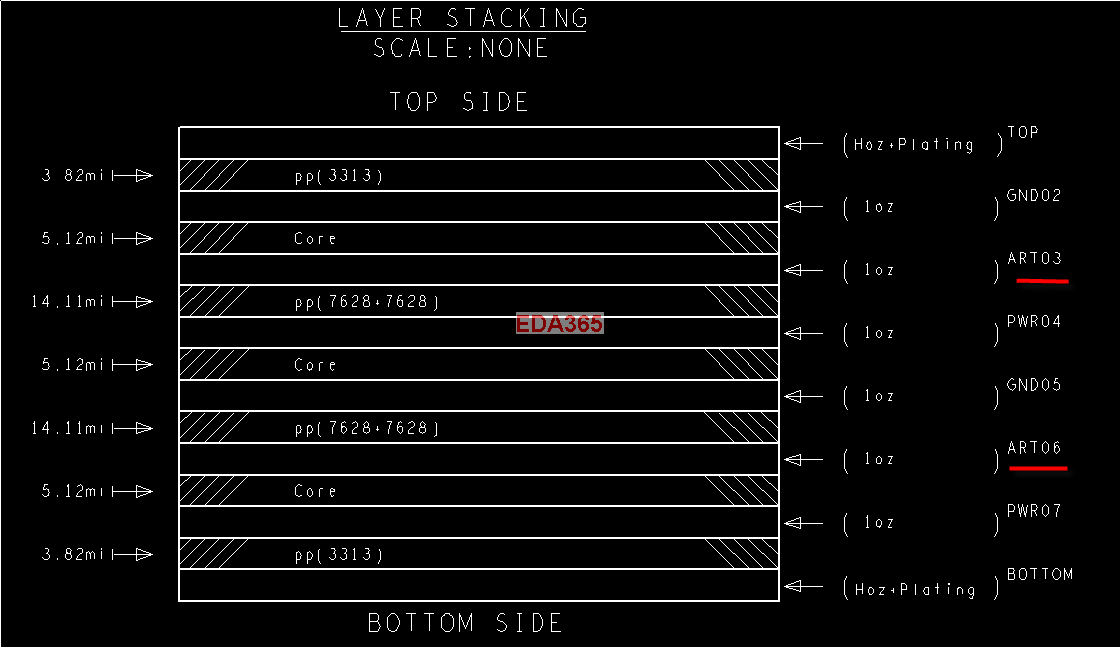

八层板:

层叠结构:TOP布线--L2电源--L3地--L4布线--L5布线--L6地--L7电源--BOTTOM布线

阻抗控制要求:

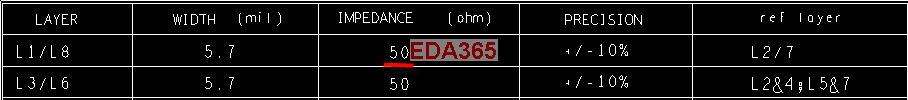

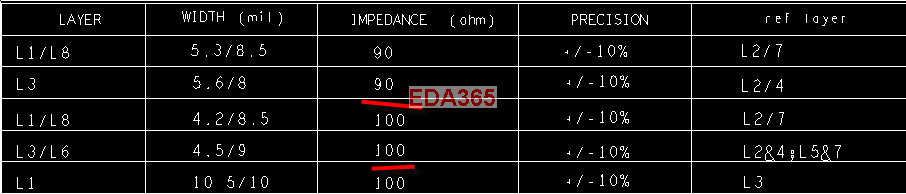

TOP:4.5mil线宽/8mil线距,单端50差分100

L4: 4mil线宽/8mil线距,单端50差分100

L5:4mil线宽/8mil线距,单端50差分100

BOTTOM:4.5mil线宽/8mil线距,单端50差分100

层叠说明:

L3和L6为地层,目的是为L4和L5层做好屏蔽和参考。设计的初衷是L4层和L5层之间间距很大,保证L4和L5上的信号互相不会干扰。

请问这样的层叠结构是否可以实现上述阻抗控制要求。

谢谢大侠们。

另外,请教一个问题,cadence中阻抗计算结果和si9000的阻抗计算结果差距有多远呢?

不能同时满足差分阻抗100欧姆和特性阻抗50欧姆喔,因为如果满足100欧姆,其特性阻抗必定大于50欧姆!

lz主要稍微该店,一般式FR4的厚度,线宽,线间距三个因素控制阻抗,LZ现在规定死了两个,只留一个可控。

1.6mm板厚这样的叠层比较常见。可以参考一下。

单端线;

差分线;

如果电源不多,容易处理,电源层可以改为地层。

关于叠层设计:

个人觉得是 层数 和 板厚 来决定 线宽 和 间距,不是规定线宽和间距来考虑叠层。

用SI9000,但不同的厂家参数会不同,这个需要跟厂家沟通,他们都会有相关的技术文档的。

多谢各位,就是电源比较多,两个电源层都有分割。外层4.5mil线宽和内层4mil线宽无法更改,倒是可以放开差分线距,这样的话应该可以实现吧?

回5楼,主要因为电源分割严重,而4和5是主要布线层,所以这样考虑叠层的。

这里继续请教另外一个问题:我所有层都是positive的,今天产生gerber之后发现via全部和所有电源层连接一起短路了,回cadence观察同样是连接到了一起,悲剧的是修改space约束thru via to shape一点也不起作用,请问这会是什么原因呢?

这个没遇到过,怪异,出gerber报错否?

1:避了铜皮没

2:gerber参数可能不对。

先抱怨一句:论坛太慢了,比上国外网站还慢,晕。

正题~

这个问题解决了,重现编辑了一下过孔然后更新就行了。因为全是positive,删除了过孔的thermal和antipad。不知道是不是因为他们的影响,不过总算正常了。

会楼上两位,gerber生成不抱错,gerber参数是正确的。

花环盘和隔离焊盘不影响正片的

那个参考叠层的信号层都有完整的GND相邻,电源层不夸特别重要或高速的信号,还是不错的。

0.8mm焊盘改为16mil-8mil,顶层线宽设计为5mil,顶层阻抗54欧,基本满足要求了~

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:高手来帮忙下,PCB问题

下一篇:DDR2源端端接电阻,阻抗匹配,板子加工