- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于走线跨分割的问题

录入:edatop.com 点击:

1. 什么是走线跨分割?

2. 所谓的跨分割是走线针对地平面还是走线针对地以及电源平面呢?

3. 一般地平面很少需要分割,而电源常常需要分割,需要注意什么呢?

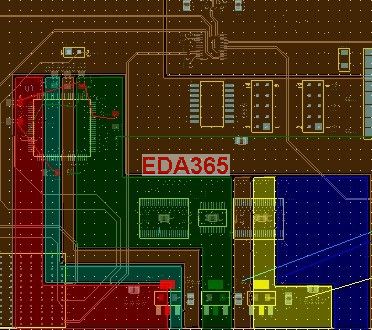

比如上图中,有高速差分时钟等差分信号跨过了分割,具体会有什么影响呢?

上图就是叠层关系,现在是Lyr11有分割,而Lyr10是一个完整的GND层,这样bottom上的走线(如2楼图)是否还存在跨分割的问题呢?

2. 所谓的跨分割是走线针对地平面还是走线针对地以及电源平面呢?

3. 一般地平面很少需要分割,而电源常常需要分割,需要注意什么呢?

比如上图中,有高速差分时钟等差分信号跨过了分割,具体会有什么影响呢?

阻抗不连续,回流路径可能变长,怎么处理还真不好说,一般没怎么处理,,跨地的时候可以加个磁珠、电阻之类吧,个人意见,高手批评补充

多谢你的回复,2楼图中分割的是电源层,看到的走线是相邻信号层(底层),另外在该电源层的上面还有专门一层地,但是与底层之间还隔着这个电源层,所以我想底层回流应该优先找这个被分割的电源层吧?如果这样就存在跨分割的问题。

上图就是叠层关系,现在是Lyr11有分割,而Lyr10是一个完整的GND层,这样bottom上的走线(如2楼图)是否还存在跨分割的问题呢?

我不明白的是,bottom层为什么要走线呢,内层那么多走不完吗?top层和bottom层一般不是指用于摆放元器件、焊接、fanout等吗

我表层不但走线了,而且还走了很多线:

如果只是针对阻抗线的差分信号跨过了分割,你可以把Lyr10与Lyr11交换应该就可以了,但是如果有针对EMI的差分信号跨过了分割,这个比较麻烦!

我注意关注阻抗一致,EMI本系统不考虑。

你的意思让GND靠近bottom,其他我也想过,但是问题依然存在于倒数第三层,即Lyr9层。

加层

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:16.2差分与其它NET的20MIL间距规则设置

下一篇:请教如何建零件库