- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

请高手指点,动态铜皮不避让问题

用的是cadence16.3 ,表层想铺GND,铺的动态铜皮竟然没避让,奇怪的是只有top层出现这种情况,bottom正常,datebase check后,仍然有这种问题,是软件Bug吗?

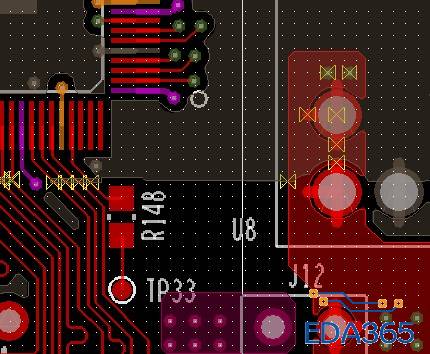

如图

中间空白处也没铺进去,还有不该铺进去的铺上了,黄色DRC错误

那位好心人帮忙解决下,谢谢

shpe ——select shape 选择那个没有避让的shape后右键rise priority

第一步确定你的铜皮是动态的,第二不点击move点击那个铜皮然后ix 0 回车 一下就可以了。我在做的时候也经常遇见这样的问题,不过是铜皮和np孔keepout上的问题,具体是是不是软件的bug 不晓得!

·

第一步确定你的铜皮是动态的,第二步点击move点击那个铜皮然后ix 0 回车 一下就可以了。我在做的时候也经常遇见这样的问题,不过是铜皮和np孔keepout上的问题,具体是是不是软件的bug 不晓得!

我猜猜應該是因為您是直接鋪大銅面所引發出來了.

您可試著把原有的銅箔予以刪除 , 然後用小銅箔來鋪大銅面應該就會解決了.

您的意思是一小块一小块的铺,这样确实没问题,但是令我费解的事,同样大小的铜皮,bottom就可以,top就是不行

如果可以你把板子发上来估计很快就解决了……

选择smooth,然后update shape!

文件发不了,抱歉,smooth一下就找不到铜皮了

正片负片对不对?我上次搞错负片,也差不多这样情况

你开一下你顶层的boundary,看看是否有重复的铜皮

同12楼

谢谢高手的指点,根据您说的,我将所有层的boundary都打开,删除整个PCB shape

重新铺铜,最终还是那个地方报错,不避让铜皮,跟原来一样

实在没办法,我先将那个器件删除,update shape,OK没问题,然后从place -manual 、

重新放置器件,铜皮就避让了

可能之前有操作不当的原因,单位转换后,update symbol

顶一下 目前遇到同样的问题 求原因

莫非真的是软件bug?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:问一种器件的贴片工艺问题

下一篇:建立焊盘出现下面问题,如何解决?