- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

求助:关于ddr3的布线规则

录入:edatop.com 点击:

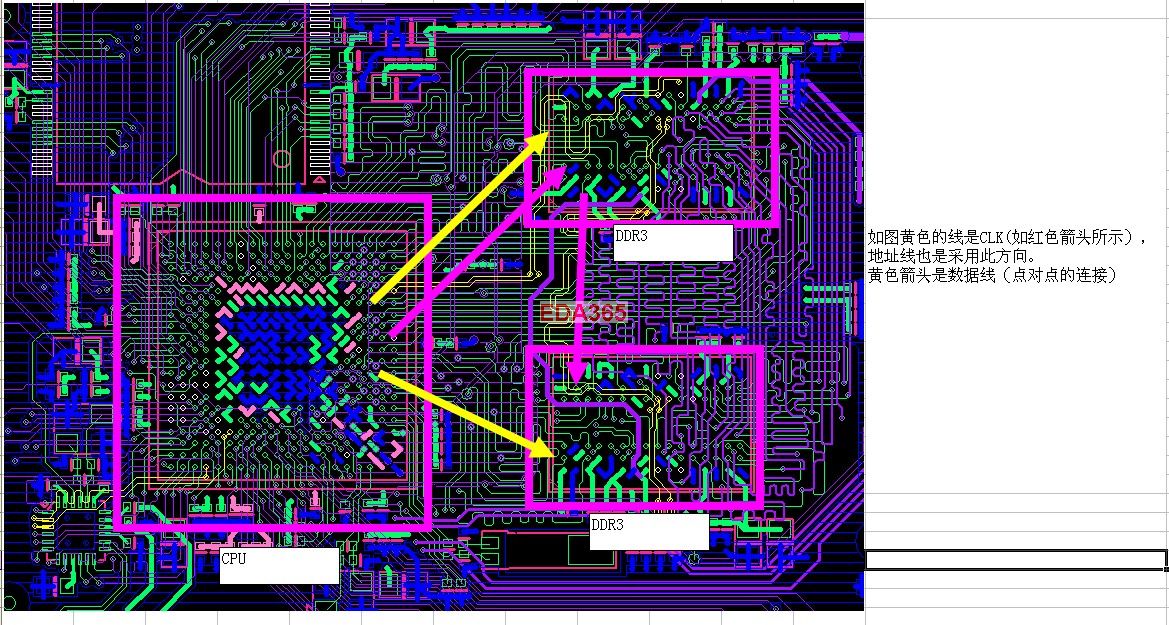

今天布了一块dd3的板子,板子的走线的拓扑结构是fly-by的结构。但是在绕等长的时候出现了困惑。

问题主要是在绕clk线。开始的时候我是按照地址的走线的方向,即线先从CPU到上面的一片的ddr3,然后再拉到另外一片ddr3.但是发现这样到另一片的ddr3的长度比CPU到另外一片的数据线长了很多,如果绕数据线,下面的数据线将很长?请问关于fly走线的情况下,clk长度是如何匹配的,CLK的走向是同地址走flyby的方式呢,走T型的,希望大家帮忙解决。

如图:

问题主要是在绕clk线。开始的时候我是按照地址的走线的方向,即线先从CPU到上面的一片的ddr3,然后再拉到另外一片ddr3.但是发现这样到另一片的ddr3的长度比CPU到另外一片的数据线长了很多,如果绕数据线,下面的数据线将很长?请问关于fly走线的情况下,clk长度是如何匹配的,CLK的走向是同地址走flyby的方式呢,走T型的,希望大家帮忙解决。

如图:

我对DDR的理解都是走T型。因为如果走菊花链,这样地址组必然寻址时间不一样。而数据的读写前要进行寻址,这样就会引起读写操作的不同步性。

但是很多文献说要走菊花链,就如你的DDR3。我是新手,也搞不懂,希望大家讨论一下吧

这个可以看下chipset的guideline,里面会有提到

那里能找到?

如果是菊花链的拓扑,两片DDR3的布局就不能对称。LZ的这种摆放明显更适用于T型,地址线/时钟从CPU出来在T点打孔,分别到两片DDR3,VTT电阻就从T点的过孔引出。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:VIA做了FLASH后,为什么在PCB中就是更新不了呢?

下一篇:求高手帮忙:点padstack 路径怎么没反应呢?