- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

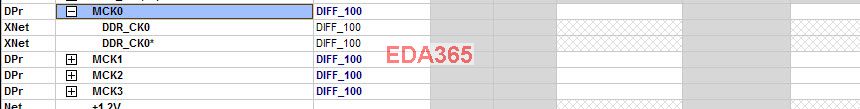

差分线线距设置

普通线线宽4,线距8,差分线线宽5,线距9的时候是不会有DRC错误的。

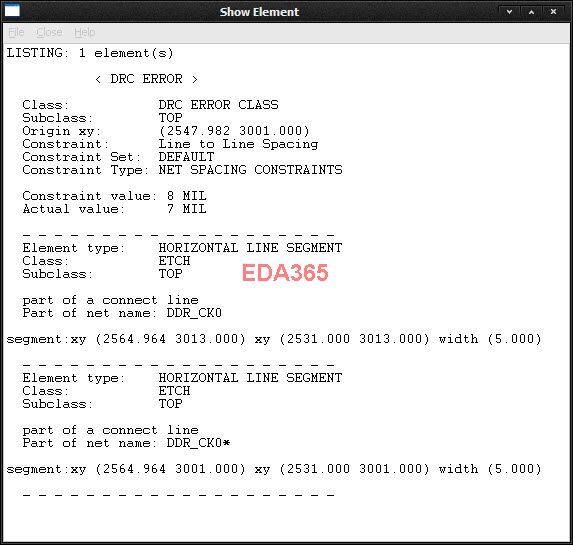

但是若将差分析啊的线距改为7后,就出来DRC错误,图如下:

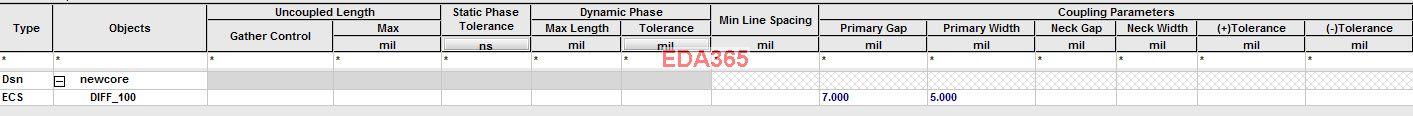

差分线的规则是用ECSET设置的,修改primary gap来设置差分线线宽和线距,然后对差分线赋予该ecset。

当差分线线距为9的时候,差分线走线出来的间距是9,那么不是说明差分线的规则优先于普通线的,这很好理解。

当差分线线距为7的时候,差分线走线出来的间距是7,但是悠然drc出错,这个不好理解了,请高手帮忙解释一下。

我猜差分线的primary gap只是设置了走差分线时软件设置的两线距离,检测间距drc只使用普通线与线之间的规则,毕竟查分线有neck 模式,如果以primary gap作为距离检测依据,neck模式也会报错,如果以neck 间距作为检测依据未免太小,用哪个都不合适,并且无论用哪个,这个间距规则就定死了,不灵活,反正allegro能够对单条走线的规则进行修改,这个不是大问题。

drc那个报告已经告诉你问题出在哪里了吧?

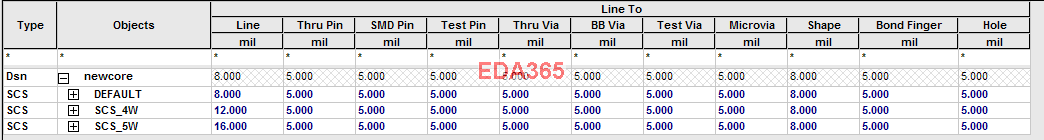

你的scs设置的有问题

不对的,scs设置的是差分线对对别的线的间距,不是差分线对内两线之间的间距,我说的这个问题,scs应该是管不上的。

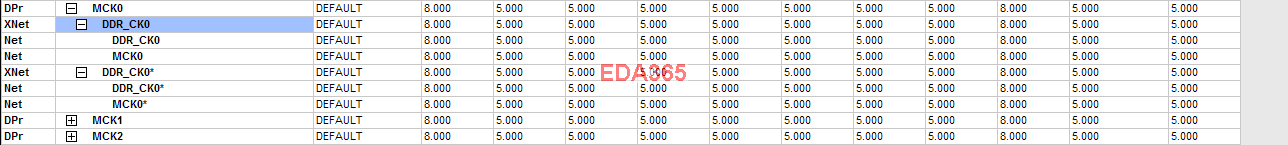

你查看一下,你的sce里面,是不是把线的规则设为了default

你说的对,scs是设置为default,因为需要将差分对线和其余线的间距设置为3w。如下两图:

差分线的内距设置如下两图,只要将DIFF_100的7改为9就不会有错。

哪位高手帮忙解决一些,谢谢。

你的线间距设的是8,差分线线间距又没特殊定义,系统按默认来识别,你的7就报错了。你可以修改差分约束里的线间距改为7就行了,叫primary gap的值。

这个已经设置了,如6楼的第1、4图

哦,你在space中的net选中DIFF—100把default改成小于7就行了。

我要疯了,你在说啥。

space中的net使用的是space cset,DIFF_100是electrical cset不是同一类约束;

default的值为8是因为所有线的线距要保障3w(除差分线内距),所以当然不能修改;

我的问题是,如何能使得差分线内距小于default的线距而不报drc?谢谢

你选中NET中的LINE,把你的差分对默认值都改成小于7就不报错了。

注意那个min line spacing,如果你填0的话就是用space cset的值作为约束,如果填写一个非0值,则以这个值作为约束!你的min line spacing是空的!

你把min line spacing写入7就不报错了,如果您还设置了neck gap,min line spacing不能大于neck gap,和我猜的差不多,primary gap数值并不作为两线间距约束依据

我不明白你为什么一直在ecs里面设置差分规则,当然我好久之前在论坛里有帖子说,差分规则只能在ecs里面设置。

如果这样的话,pcs里面定义差分线规则就没用了。尽管我没搞懂这两个的区别。

你可以试一下,在pcs里面建立一个diff—100,min line width设置为5,min line spacing设置为你所谓的7,然后把差分线赋予该pcs。

试试看吧

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro里面的有些封装为什么要画flash symbol

下一篇:请教问题:如何设置Allegro输出光绘文件的路径?