- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

allegro阻抗计算有BUG

录入:edatop.com 点击:

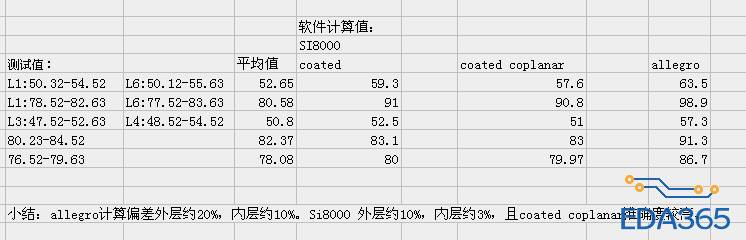

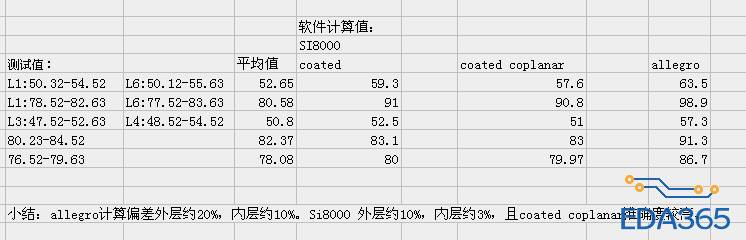

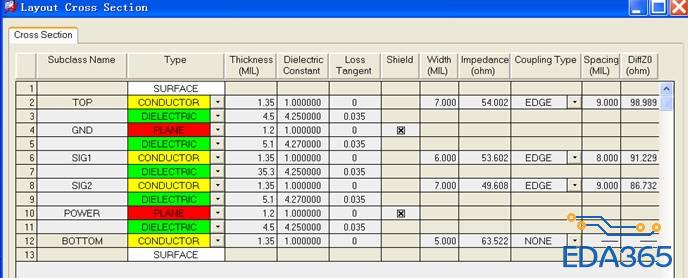

不知道有没有人发现,allegro阻抗计算值比实测大,表层大15%-20%,内层大10%。做仿真时是不是要调整叠层参数来补偿这个差值?

allegro不准的!阻抗计算的时候底下就说明的是用公式算的!只做参考,仿真最好做上补偿!

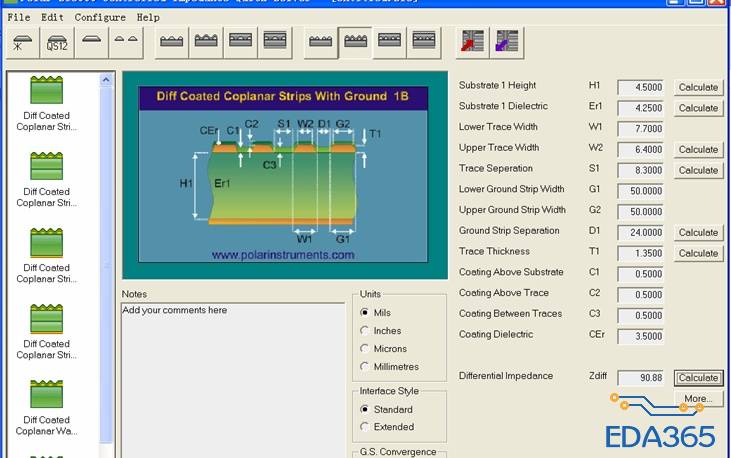

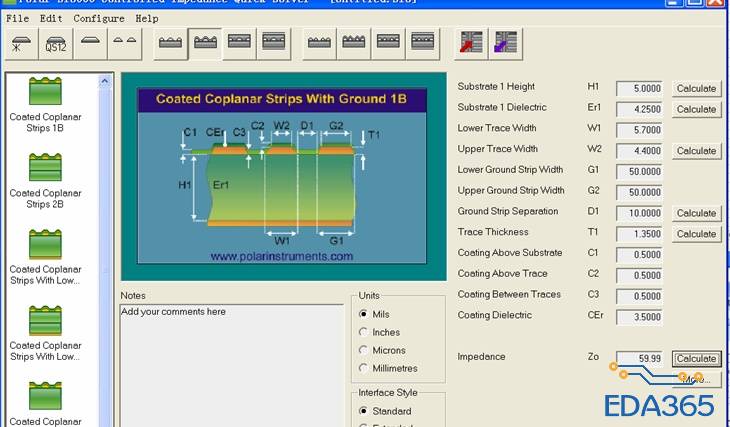

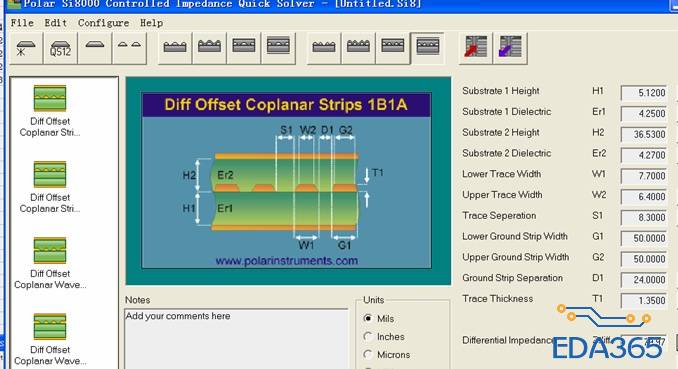

polor伺候

怎么补偿?线宽,介子厚度,介电常数?调整这些参数是可以补偿阻抗,但会不会使其他仿真不可信,如串扰仿真。

PCBSS上有人说计算和测量结果区别小?难道是板厂给的参数不可信?

polor计算也偏大,但没有allegro离谱。

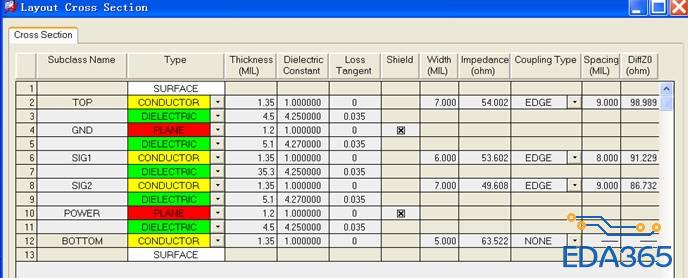

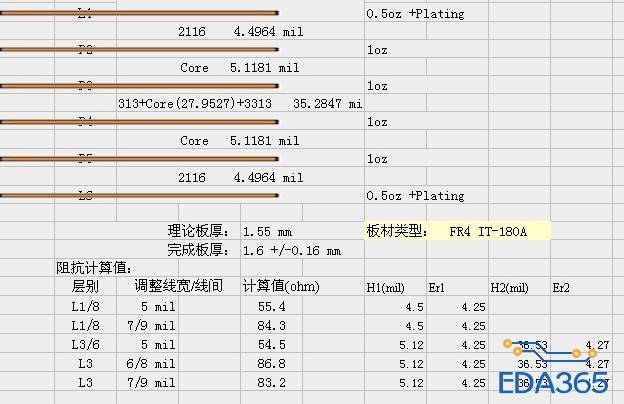

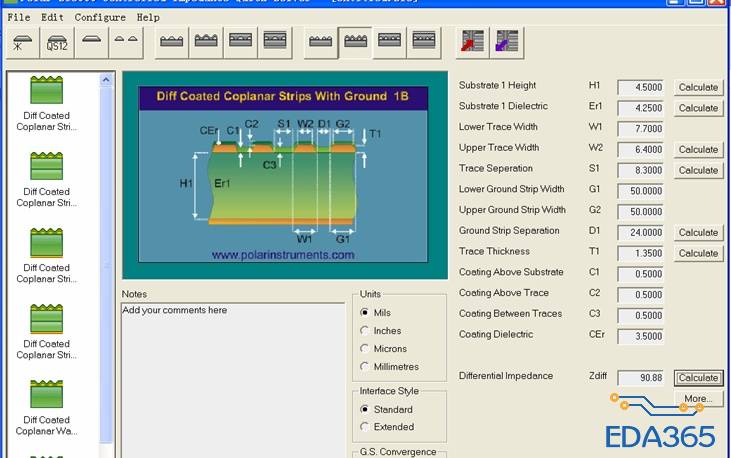

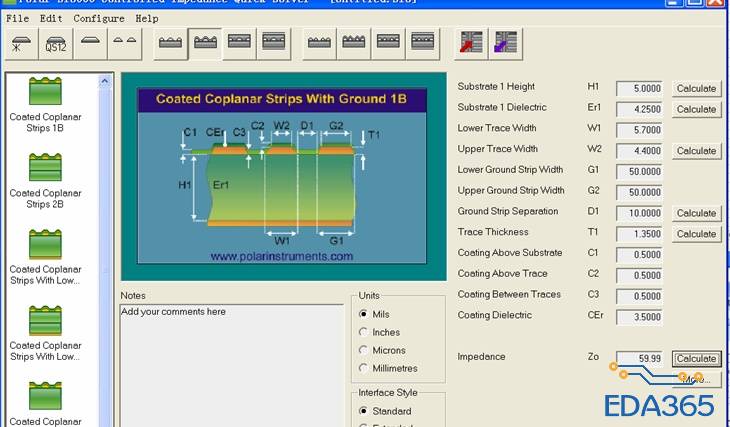

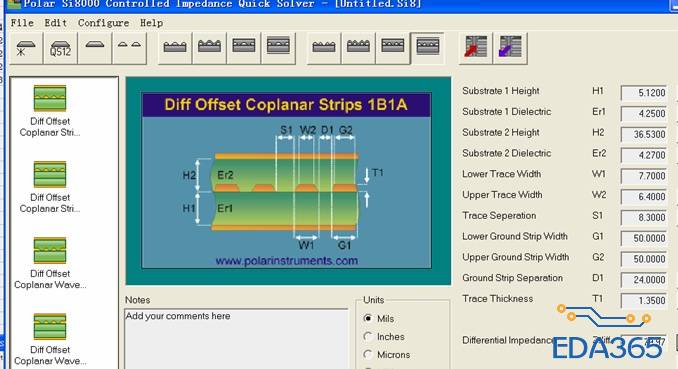

这是板参数,测试值,计算值。请大家看看哪里有问题,w1/w2/c1/c2/c3/cer都是板厂给的调整要求

只要相差不大就行,

数字信号允许有较大的变形,仿真的时候将振铃的幅度、上冲、下冲控制在比较小的范围内就行。

SI8000结果相差10%,allegro结果相差20%,这个不能计算吧

对的 测量也未必完全准确 只能找到一个定向的范围

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:元件布局,求助~

下一篇:制作flash保存时出错,请教高人