- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

2层PCB中PCIe-x1的100欧姆阻抗控制设计

录入:edatop.com 点击:

根据PCI-E标准要求,PCI-E差分信号线要求差分阻抗为Zdif=100,Zcom=60。2层板设计也必须满足这个条件,现在板层参数如下:

铜线厚度T:1oz,大概1.4mil厚

板厚H:1.5mm ~= 59mil

介质:FR-4,2116,电介参数E~=4.2

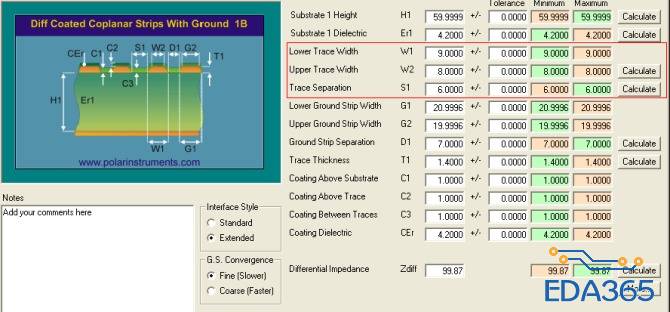

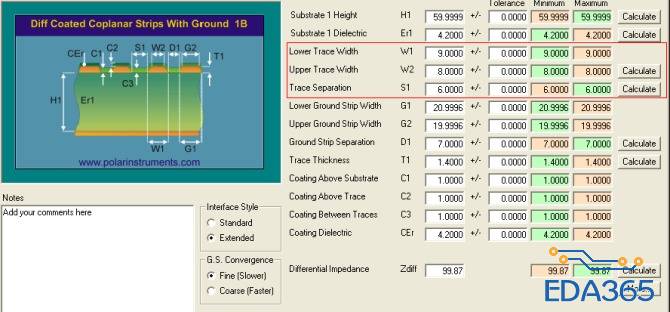

采用耦合微带线方式layout,通过Polar Si9000计算参数如下:

从图中可以看出,差分阻抗为Zdiff=99.87,满足设计要求,即要求线宽为9mil,线距为6mil,外围包地安全距离为7mil。差分线对于其他差分线对之间的距离>=24mil,这里我们取>=40mil。详细参数如下:

过孔设计参数:内径=14mil,外径=25mil。

铜线厚度T:1oz,大概1.4mil厚

板厚H:1.5mm ~= 59mil

介质:FR-4,2116,电介参数E~=4.2

采用耦合微带线方式layout,通过Polar Si9000计算参数如下:

从图中可以看出,差分阻抗为Zdiff=99.87,满足设计要求,即要求线宽为9mil,线距为6mil,外围包地安全距离为7mil。差分线对于其他差分线对之间的距离>=24mil,这里我们取>=40mil。详细参数如下:

过孔设计参数:内径=14mil,外径=25mil。

PCI-E 2层板很难搞的吧!

LZ能不能大概计算一下4层板的阻抗:板材为常见的KB。

我的项目参数如下:

线宽为6mil,线距为6.5mil,外围包地为30mil.

过孔设计参数:内径=12mil,外径=24mil

LZ能不能帮计算一下这个能不能满足?

我已经打样过了,PCIE差分线最长有30CM长,基本没换层,实践能稳定运行!

我想知道理论计算出的和实际的差别。

谢谢!

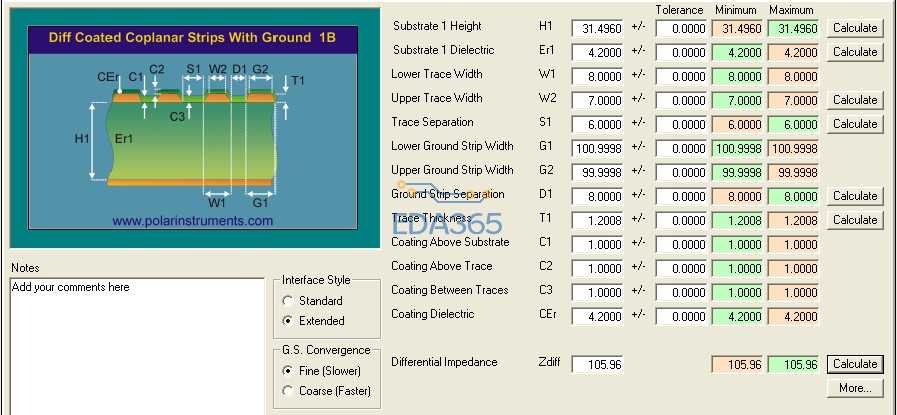

根据小编的参数,计算了下,见下图:

看到了!Zdiff=119了,似乎误差还比较大了 ! 不过实际也能稳定运行的。

恩,是的,应该问题不大

请问搂着这套设计参数有没有实际用于2层板的制板中?有的话实际效果如何? 这边用这套模型算的0.8mm厚的2层板数据打板,板子回来后,pcie怎么都link不上,不知道是什么原因。

pcie双面板也可以?

我的板子可以,你的板子厚度是否涉及到位了?

把板做溥

底层铺铜完整不?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:求解:主板 右边缘 螺丝孔 只有半圈焊锡 的用意,感谢各位,再拜个晚年!

下一篇:ALLEGRO 同一个网络过孔打到焊盘上怎么让他不报错?(有图片)