- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

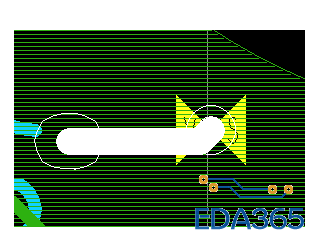

DRC 問題

录入:edatop.com 点击:

Class: DRC ERROR CLASS

Subclass: GND

Origin xy: (14084.40 9974.80)

Constraint: Shape to Thru Via Spacing

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

Constraint value: 5 MIL

Actual value: 0 MIL

- - - - - - - - - - - - - - - - - - - -

Element type: VIA

Class: VIA CLASS

origin-xy: (14084.40 9974.80)

part of net name: IO_GND

Connected lines: 1 ( TOP )

Connected shapes: 1 ( VCC )

padstack name: VIA18D10

padstack defined from TOP to BOTTOM

rotation: 0.000 degrees

via is not mirrored

请帮忙看一下,这个DRC 问题怎么解决,我是新手,谢谢。

Subclass: GND

Origin xy: (14084.40 9974.80)

Constraint: Shape to Thru Via Spacing

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

Constraint value: 5 MIL

Actual value: 0 MIL

- - - - - - - - - - - - - - - - - - - -

Element type: VIA

Class: VIA CLASS

origin-xy: (14084.40 9974.80)

part of net name: IO_GND

Connected lines: 1 ( TOP )

Connected shapes: 1 ( VCC )

padstack name: VIA18D10

padstack defined from TOP to BOTTOM

rotation: 0.000 degrees

via is not mirrored

请帮忙看一下,这个DRC 问题怎么解决,我是新手,谢谢。

issue

Shape to Thru Via Spacing

铜皮到孔的距离应该大于5mil,而你是0,短路了.

这个怎么修改 能帮忙讲一下吗?谢谢

你那个是短路了.孔和铜皮应该不是同一个网络名.

如果是不同网络,你讲动态铜升级看看,如果你已经设置了静态铜您就像过孔附近的铜片删除吧

如果你铺的是动态铜箔,你跑一下drc会自动闪开的,如果你铺的是静态铜箔,你可以选择命令shape--manual--void,然后框住过孔,静态铜箔就会在过孔那个地方闪开,如果是静态铜箔,要是还是闪不开,你就手动将包住过孔的那里的铜箔挖掉

谢谢,我重新铺的是动态铜,暂时没有问题。

请问静态铜和动态在使用时有什么区别吗?

非常感谢大家的回复。