- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

ORCAD16.5重出网表出错。

录入:edatop.com 点击:

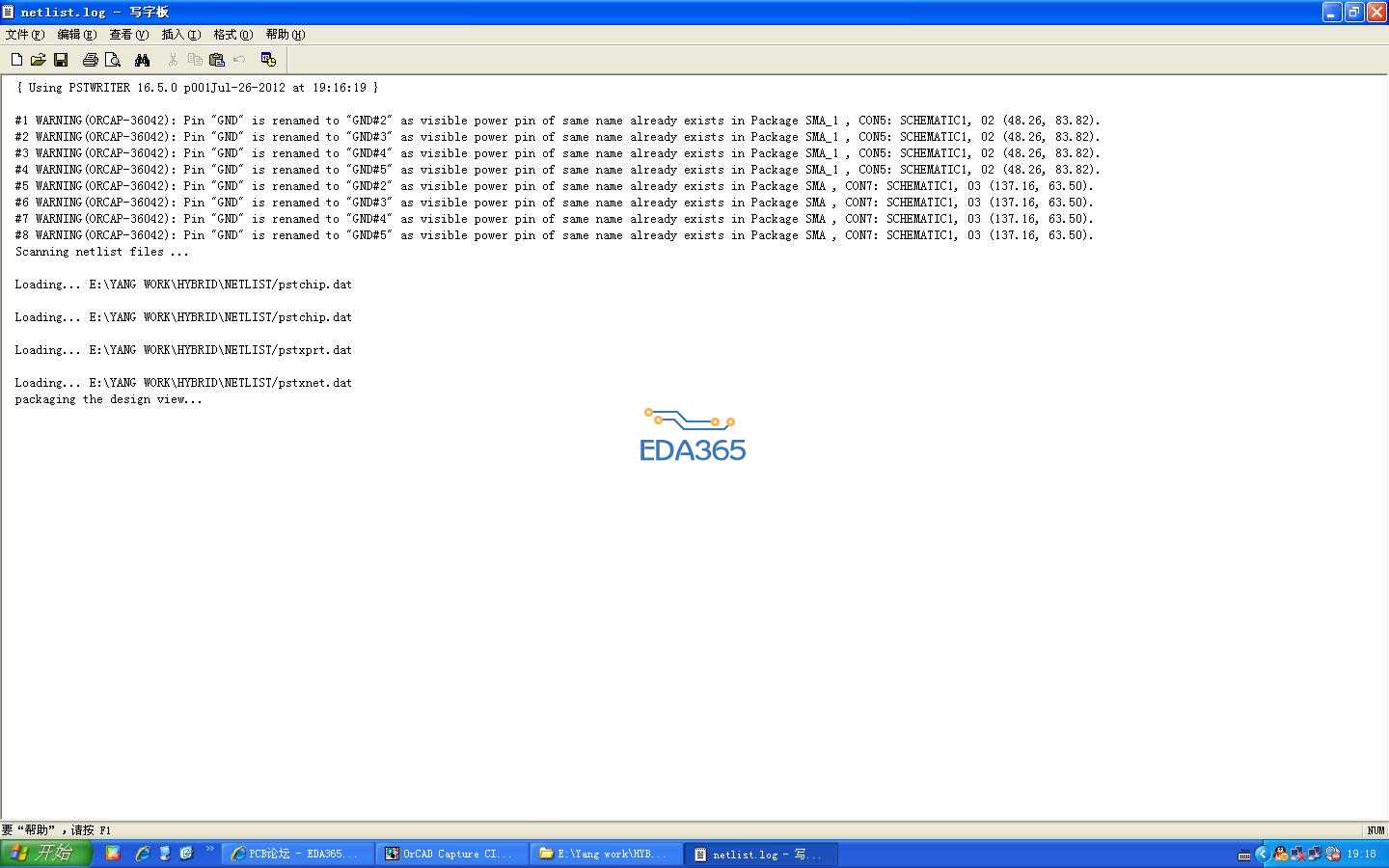

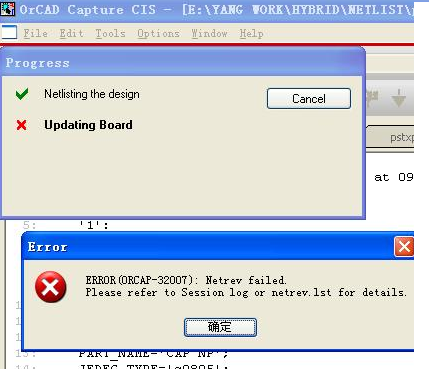

在原理图里面修改了一个元件PIN脚的属性,重新导出网表出错。

,这是怎么回事?

,这是怎么回事?

产生的原因就是主题里的。但是我不勾选Creater or update pcb editor Board(netrev)可以正常出网表。

说的太粗了点,详细一点!

我先用原理图出过网表,后来在做PCB板子的时候。需要将一个功分器的2个OUTPUT脚交换。就回原理图将2个OUTPUT脚PinGroup修改为1。准备再导出网表到allegro。如图:

产生的原因就是主题里的。但是我不勾选Creater or update pcb editor Board(netrev)可以正常出网表。

那就先用正常导出,再到allegro里,用import--logic试一下!看一下,问题是在哪个环节!

能正常导出网表,导出的网表也能导入到ALLEGRO里正常工作。完全按照第一次导出网表,再导入到ALLEGRO里,完全没问题。

不过已解决,我在原理图把2个接地引脚的PINGROUP设置成0了。现在去掉0,保存为空的。可以CREATE OR UPDATE PCB EDITOR BOARD(NETREV)。

但是还是不明白,ORCAD里面,2个接地引脚不能设置PINGROUP了?