- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于网表导入的问题

( )

( Allegro Netrev Import Logic )

( )

( Drawing : 123.brd )

( Software Version : 16.5P002 )

( Date/Time : Fri Aug 10 16:05:54 2012 )

( )

(---------------------------------------------------------------------)

------ Directives ------

RIPUP_ETCH FALSE;

RIPUP_DELETE_FIRST_SEGMENT FALSE;

RIPUP_RETAIN_BONDWIRE FALSE;

RIPUP_SYMBOLS ALWAYS;

Missing symbol has error FALSE;

SCHEMATIC_DIRECTORY 'G:/candence/unrouted';

BOARD_DIRECTORY '';

OLD_BOARD_NAME 'G:/candence/unrouted/123.brd';

NEW_BOARD_NAME 'G:/candence/unrouted/123.brd';

CmdLine: netrev -$ -i G:/candence/unrouted -y 1 G:/candence/unrouted/#Taaaaaa08836.tmp

------ Preparing to read pst files ------

#1 ERROR(24) File not found

Packager files not found

#2 ERROR(102) Run stopped because errors were detected

netrev run on Aug 10 16:05:54 2012

COMPILE 'logic'

CHECK_PIN_NAMES OFF

CROSS_REFERENCE OFF

FEEDBACK OFF

INCREMENTAL OFF

INTERFACE_TYPE PHYSICAL

MAX_ERRORS 500

MERGE_MINIMUM 5

NET_NAME_CHARS '#%&()*+-./:=>?@[]^_`|'

NET_NAME_LENGTH 24

OVERSIGHTS ON

REPLACE_CHECK OFF

SINGLE_NODE_NETS ON

SPLIT_MINIMUM 0

SUPPRESS 20

WARNINGS ON

2 errors detected

No oversight detected

No warning detected

cpu time 0:00:19

elapsed time 0:00:00

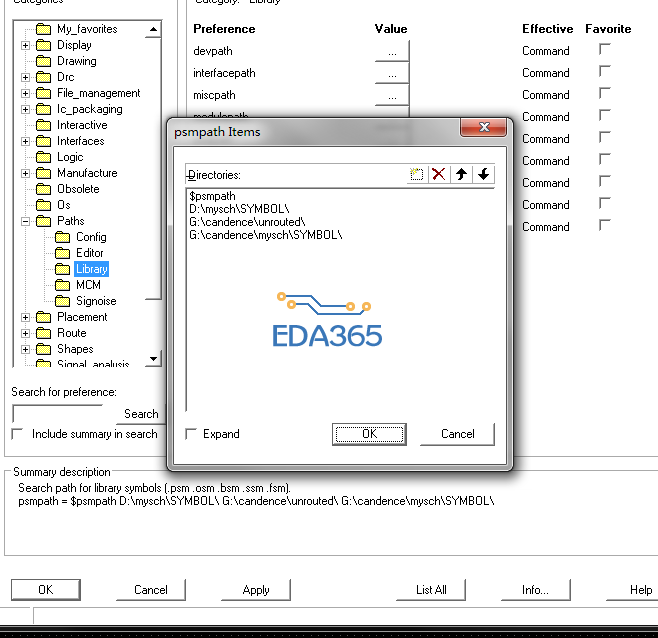

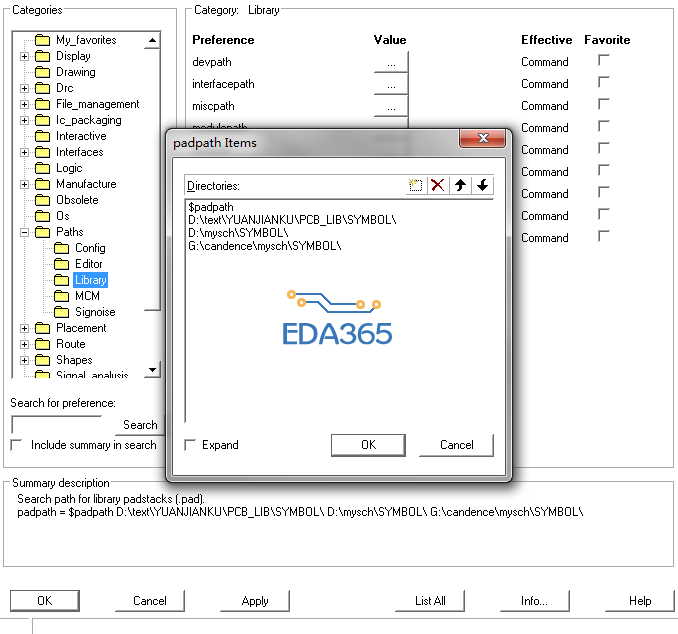

我的网表导入后出现了现在的 问题,路劲什么的都设置了,不知道怎么回事啊,急死了啊,求指点

就是因为pcb封装文件找不到,你仔细检查下吧。

你好,封装路劲我已经设置了啊!

allegro要建立原理图对应的封装,

仔细检查引脚, 仔细检查焊盘,

新建一个.brd文件, 首先要把电路板板框画出来,然后再导入capture的netlist

如果封装已完成,引脚没错, 电路板板框已完成, 路径设置完成,仍出现上面的

ERROR(24) File not found3 }+ Packager files not found

那仔细检查焊盘,

请问怎么检查啊,还有我的焊盘不显示网表是怎么回事啊

在find选项中勾上pin、net然后鼠标指到相应的脚就可以看到你实际的pcb封装管脚是什么了。

不能直接在管教什么显示吗

肯定是封装的问题,路径的设置要对,而且PAD文件都要放进去

可以啊,你要它总是显示的话,首先在原理图中生成器件时就要设置为引脚可见,然后在pcb editor中在display---color~~中去勾上器件显示就行了。

怎么设置啊,详细点呗,找不到啊

1.在orcad中打开library,选择你要设置的器件,比如我设置的是AD5024,打开AD5024器件,option——part properties ,点击pin number visible 在最下面的小框内选择ture——ok。

2.然后生成网表,在allegro中导入刚才生成的网表,接着display——color/visibility——stack up 勾上pin这一栏。

学习

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro15.5的DRC问题

下一篇:差分布线求解,急