- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

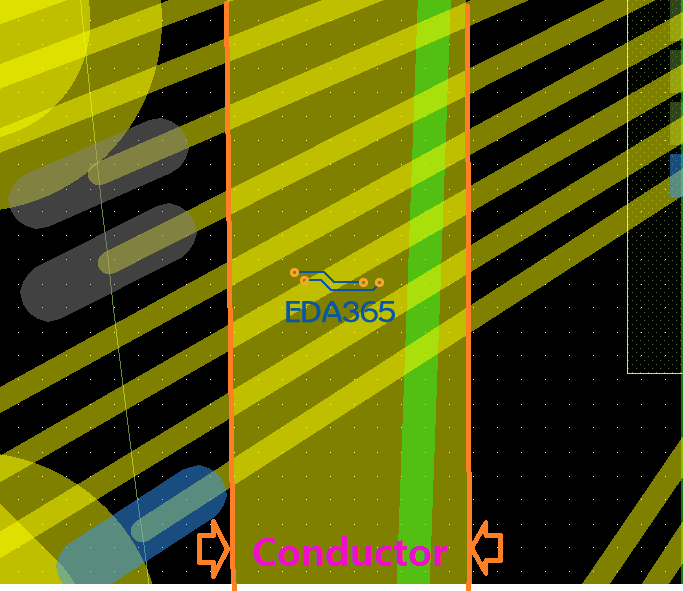

关于Candence SiP中Conductor线宽修改的问题

录入:edatop.com 点击:

由于Conductor线路跨度比较大,又考虑到约束的问题,所以想修改局部Conductor的宽度,把个别的Conductor变窄一点。

哪路大师可以帮忙解答。谢谢

哪路大师可以帮忙解答。谢谢

哇。做封装》?牛XX呀

做封装的好还是PCB好?

PCB比较容易,而且工艺也比较纯熟。封装可以达到4层、6层,再往上很困难的

有没有大师可以帮忙解惑啊,给点指导撒

PCB层数更多,模块也多,复杂吧?

如果是SIP的话,层数少,基本上就是拉线工呀。

人个看法

SiP也要考虑电源完整性和信号完整性的,而且制程能力的问题、空间的限制,6层以上的封装很困难,三批量验证都很难过关的。一般都2层、4层量产的多,封装的尺寸跟PCB比起来小多了

选上ring,右键cut就可以了

当做shape处理也行

都能解决你的问题

1000pin以上的BGA,substrate超过10层的也有,看需求了。

SIP有PI SI问题,那PCB更有这些问题了啊

这个方法没试成功,你确定那方法适用SiP的吗?

当做shape处理就OK了,封装会引入更多的overshoot,而PI方面感觉WB肯定也会更差点。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro怎样添加silkscreen_B_Topsilkscreen_B_Botto

下一篇:cadence 16.3 Allegro怎么更改丝印层的线宽