- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

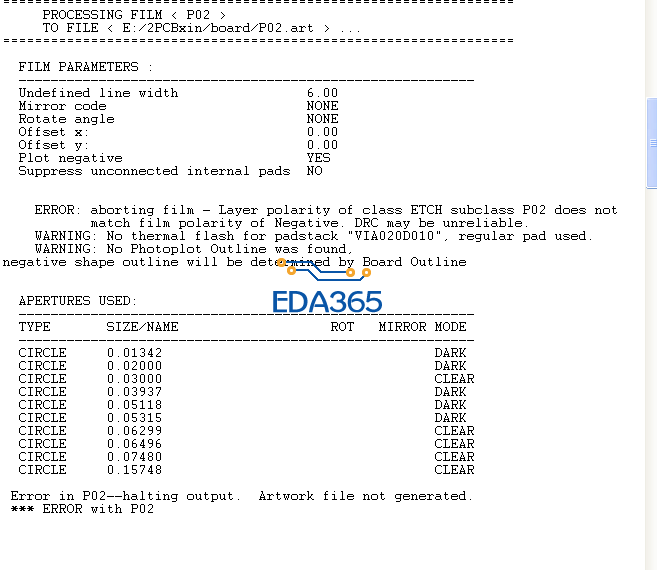

生成art文件时,查看Viewlog时发现的错误

但是我觉得自己是按步骤来的,所以对这个错误不是很理解,想知道错误的原因,希望大家指点下。

好像是你P02的正负有问题吧

用金山词霸翻译下基本上就能知道是什么问题了,呵呵

我在设置的时候,确实将电源和地都设置成了nagative,今天刚刚重新设置了一次,发现还是同样的问题。我试着继续理解错误的提示,还是想不出问题在哪里。

现在的电脑配置都已足够高了,应该不必再用负片了

在叠层设置里面, 把 Negative Artwork 和 Shield 列里面 负片层勾选就对了, 我之前也遇到过。

层叠设置的地方设置为负片,在出光绘文件的地方还需要设置为负片才行

生成art文件,errror一定是要处理的。如楼上所说叠层设置为负片,输出光绘文件设置页要为负片。

生成光绘文件时,这个warning: no thermal flash for padstack,大家是怎么理解的?

确实是这样的,需要将叠层和光绘输出中的GND和PPOWER均设置成为负片。

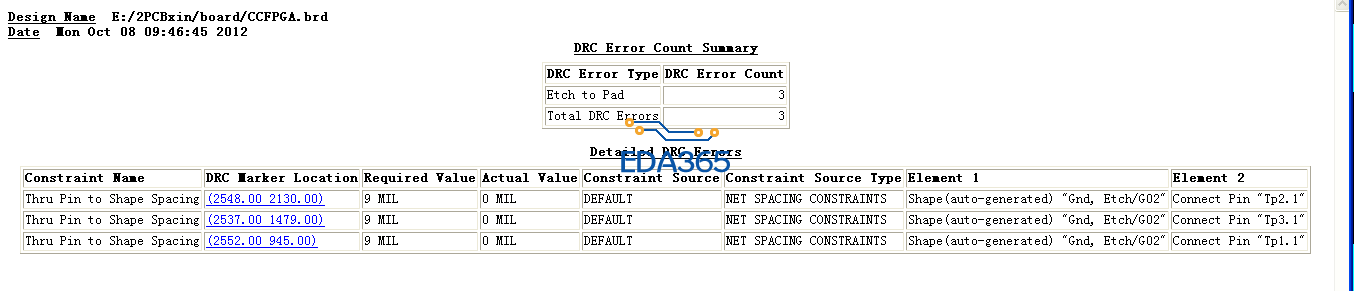

但是我这设置完成后,出现的error,是关于测试点的错误提示,如下图所示,可能这里和你所提到的warning: no thermal flash for padstack有关,我现在正在考虑这个问题。

你出现的这个错误是内电层地层铺铜与焊盘的间距出问题了,设置的约束是9mil,而实际情况是0mil。

关于生成光绘文件时,warning: no thermal flash for padstack。我问了一下同行,好像是这样的,电源层和地层如果是负片输出的话,通孔必须有热风焊盘,也就是说在pad designer里设计通孔里,在热风焊盘里需要添加flash。这个waring对最终制板的影响好像不大。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:allegro这种如何做等长,有图‘

下一篇:提示:Resolve lock file and re-run netrev,如何解决?