- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

大家有空讨论哈上下拉电阻布局有哪些讲究?

大家有空讨论哈上下拉电阻布局有哪些讲究? 我看过于博士那资料说,对于上下拉电阻的布局没什么讲究,甚至可以这么说, 当其它元器件布局好后,只要哪里放得下这些上下拉电阻就可以,大家在实际的项目中是如何处理的呢? 以及限流电阻的布局要求, 一起讨论下,共同进步。

个人感觉上下拉的布局确实没多大讲究,但是要考虑一个STUB的问题。STUB要求尽量短即可,特别是时钟更需要注意这个问题。

学习学习~

前排听课。

这个没什么影响,上拉电阻一般都取10K~100K,阻值远在导线电阻之上,而且属于静态信号,远近不是主要问题。

补充下,如果上拉电阻和下拉电阻只是为了确定初始状态或者是mode选择,没有问题。但是也要考虑布局的可操作性,比如有Mode选择的话,最好还是要就近放置,方便替换

如果是高速信号,尽量缩短分支走线的长度。

要是连接成fly_by这种形式,就用不大着考虑STUB了噻? 你觉得呢?

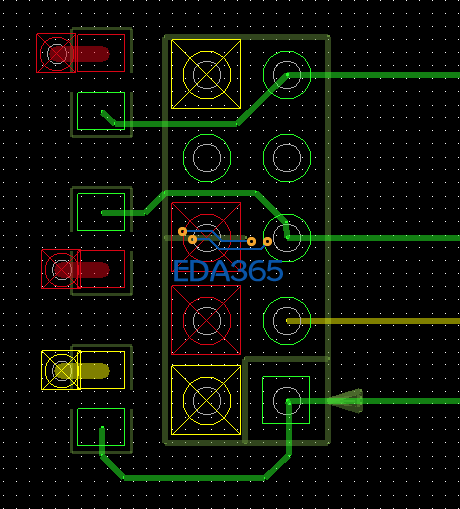

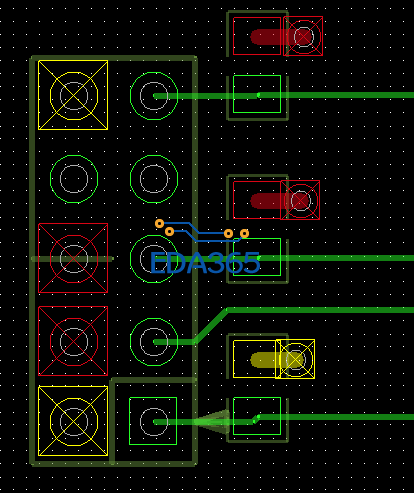

上下拉电阻这两个布局方案哪种应该优先选择呢? 大家说说自己的想法吧。 这是FPGA设计的JTAG接口

就個人認知提出一些看法: 雖然線路上都是上下拉,但功能可能不盡相同

如果是低速信號,上下拉也是一般阻值(如4.7K, 10K),這些電阻通常不重要,可以最後再放

如果是特殊的阻值,通常會影響IC內部的迴路(通常這種信號也只會單接一顆電阻),這時會希望不要離腳太遠,這種信號偶爾可能伴隨著線寬線距的設定

如果是高速信號,這些上下拉可能用於阻抗匹配,位置就要看是否有要求。如DDR,就要擺設像樓上方案一的擺法,但如VGA_RGB,就會像方案二的(還是要看trace的阻抗分佈)。

以JTAG來說,個人認為方案一的走法比較適當,但可以調整電阻位置再縮短分岔。

11楼说的很详细,可以作为参考。

时钟会用到上下拉电阻? 时钟即便是用到电阻通常也是串接一个电阻来进行阻抗匹配,这样的话尽量没有STUB...

我想知道怎样设置才能使焊盘是两个圈圈的?贴片焊盘就是一个圈的那种?

那是通孔类焊盘才有两个圈圈,里面那个圈圈表示上锡了的,Setup--Design Parameter Editor 里面,把右边的Display plated holes 前面打上钩就可以了。