- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

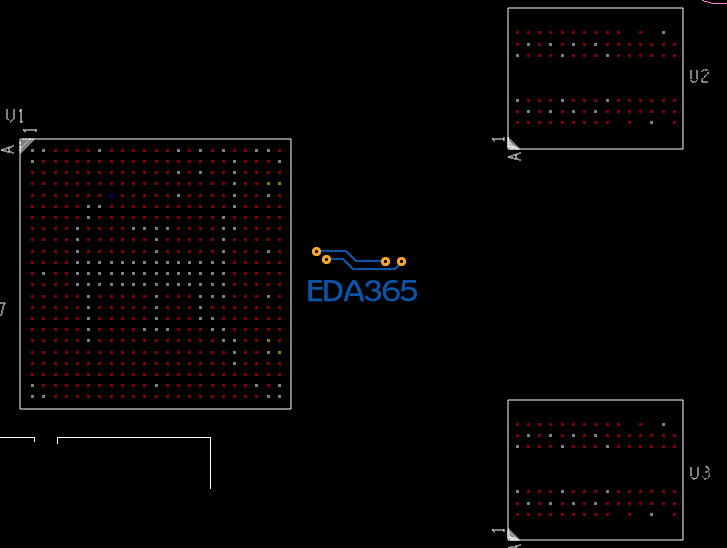

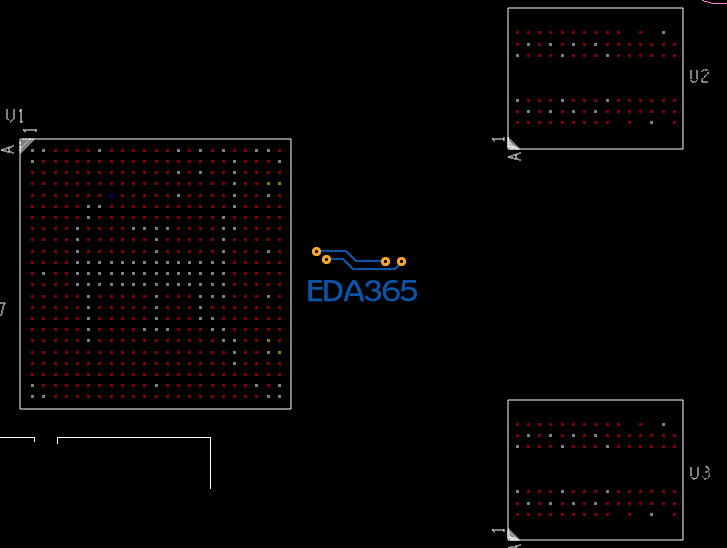

两片DDR等长问题

录入:edatop.com 点击:

一片DSP连接两片DDR2,地址线和控制线共用

请问应该如何做等长?

U1到U2、U1到U3的地址线要等长么?

U1到U2、U1到U3的控制线要等长么?

U2、U3的数据线要等长么?

以及等长的原因到底是什么?

请问应该如何做等长?

U1到U2、U1到U3的地址线要等长么?

U1到U2、U1到U3的控制线要等长么?

U2、U3的数据线要等长么?

以及等长的原因到底是什么?

u1到u2的地址线,控制线,时钟线设为一组,等长

u1到u3的地址线,控制线,时钟线设为一组,等长

u1到u2的数据线设为一组等长

u1到u3的数据线设为一组等长

等长主要是考虑并行线时序的问题

正如2楼所说的bus,等长。

其实,RAM是16位的,所以,数据线8位一组包括DQS和DM做严格等长,(+-25mil);

但4组之间也不能相差太远,一般控制在+-100mil

看看,学习一焉,稿入同!

补充问题,地址线、控制线是否以时钟线的长度为基准?误差控制在多少?

数据线以什么为基准等长?

谢谢!

是否总结为数据线同组内严格等长,不同组间尽量等长?

这个等长是以什么为基准呢?

顶一下!

数据组跟地址组之间误差应该不用控制这么严格吧,地址一般都比数据长,1000mil以内基本都能接受。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于焊盘的几个问题,希望高手指点

下一篇:SPB16.5版本的怎么设置xnet?