- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在Allegro里如何设置shape与元器件之间的间距规则?

录入:edatop.com 点击:

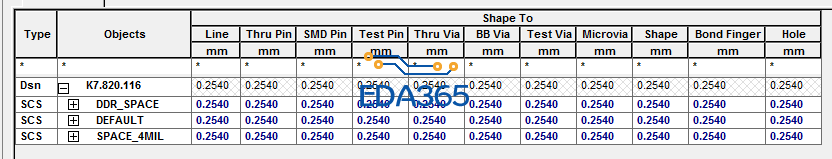

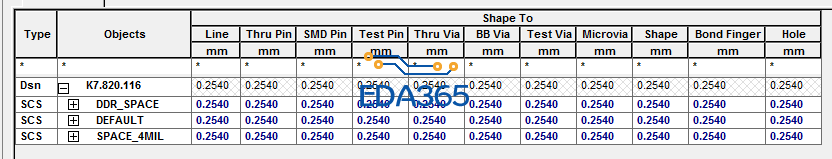

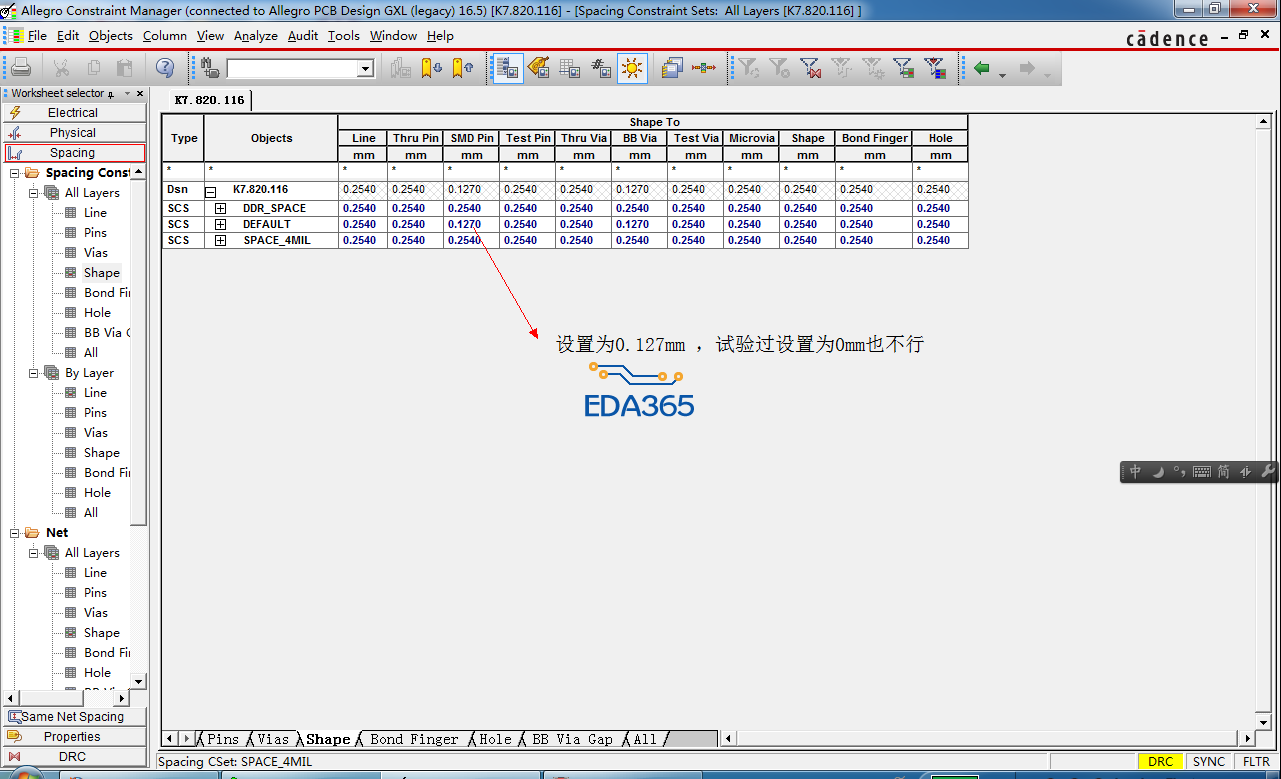

在规则管理其中,shape与其他之间的间距是10mil,如下图。

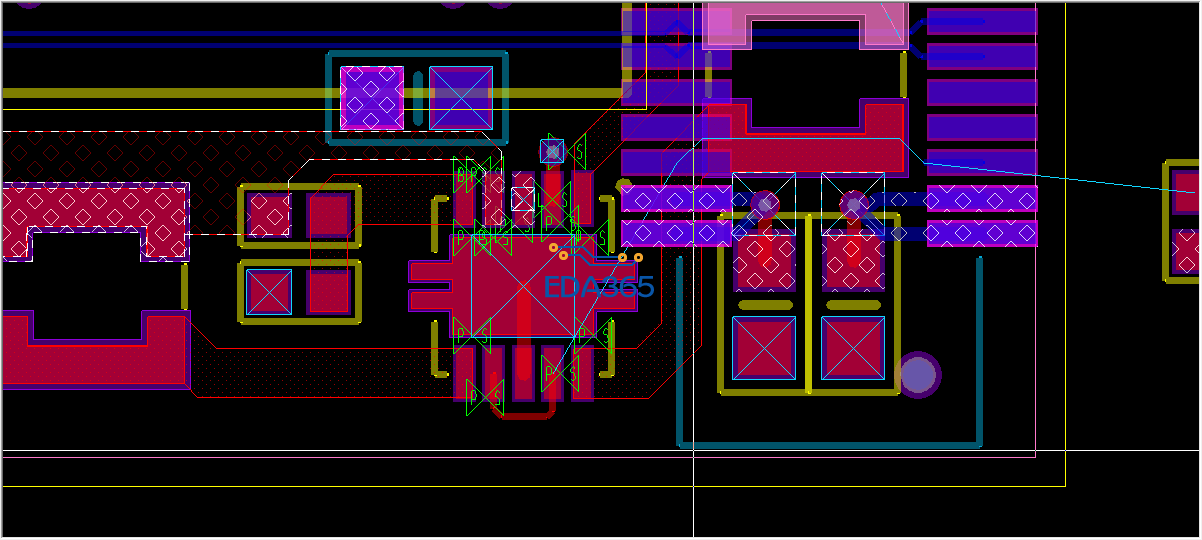

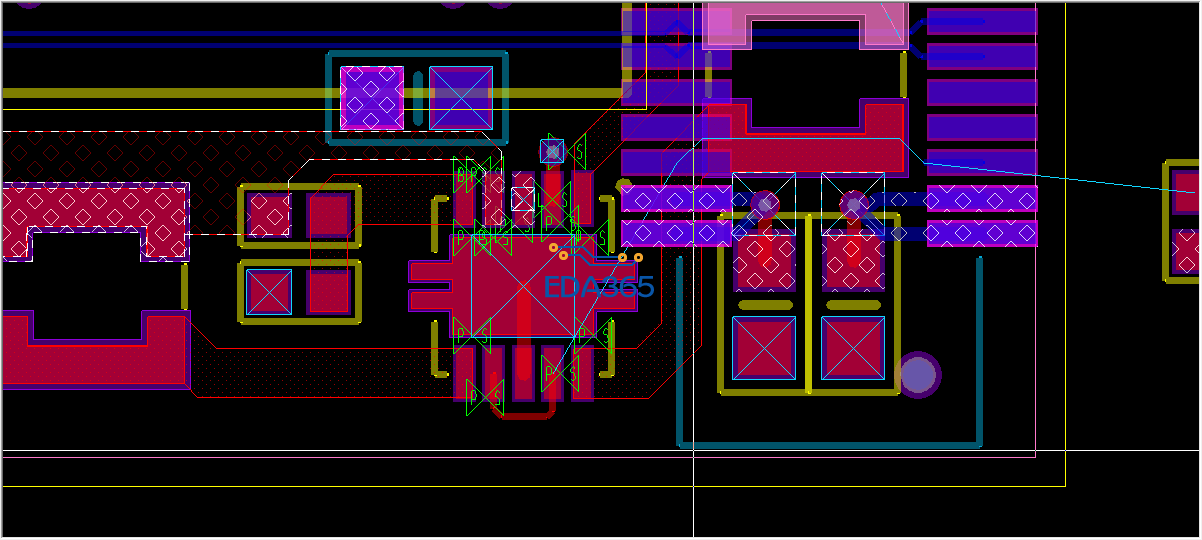

如图,图中DRC错误 “PS”。

如图,图中的走线用的静态铜。

请问,我应该如何设置规则,才能避免上图中的错误。

谢谢!

如图,图中DRC错误 “PS”。

如图,图中的走线用的静态铜。

请问,我应该如何设置规则,才能避免上图中的错误。

谢谢!

把铜皮到pin的间距设小一点就可以了

谢谢!

这样可以解决问题

但是另外一个问题随之出现,如果对整板进行铺地处理,那么就会出现铺地的铜与所有元器件的pin的间距都过小。

如果有两个shape,如何对这个两个shape进行不同的间距规则设置?谢谢!

你个鞭。用区域设置不就行了。

没有啊,你设完规则的话整版铺铜也是适用的,不过最好还是不要整版铺铜,以免出现碎铜

碎洞是什么东东?

难道不需要整板铺铜么?即使顶层不铺,中间层得铺吧?

不好意思!

即使设置了shape与pin的间距,还是不行。

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:关于热风焊盘制作的请教

下一篇:自定义焊盘的对齐问题