- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速pcb设计中,阻抗失配(讨论)

录入:edatop.com 点击:

在高速PCB设计中,经常听到要求阻抗匹配。而设计中导致阻抗不匹配的原因有哪些呢?一般又对应着怎么的解决方案?欢迎大家来讨论。

走线过程中线宽的改变、换层等都可以引起阻抗不匹配。这就要在叠层的时候计算好层厚、线宽。

赞,谢谢各位分享资料

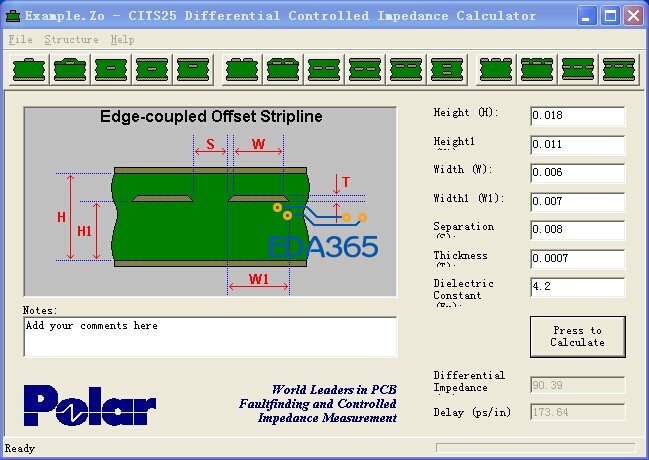

在阻抗计算器中出现的元素~线宽 线距(差分对对内间距 对间间距 单端线与周围铜皮的距离) 参考面是否完整(是否经过参考面的分割线) 铜厚 均匀程度 介质类型等等;一般除了工艺要求之外 其他的都是可以在图上通过约束和走线来实现的。

造成阻抗不匹配的原因

1、走线宽度变化,(在走线层不改变的情况下,保证走线宽度一致)

2、走线间距变化。(在走线层不改变的情况下,保证走线间距一致)

3、参考平面改变(重要信号线尽量保证从始至终参考同一个平面)

4、参考层面不连续,即中间有跨分隔情况(重要信号线尽量不要跨分隔,如果一定要跨,要在走线跨分隔位置加跨分隔电容)

5、走线换层、(重要信号线尽量不换层)

6、其他可能影响阻抗的因素就很多了,孔的大小,走线中串的电阻等等,

還有更重要, 但很多人都會忽略的 Padstack 也會有這個問題.

可以針對這個多一些解說嗎?謝謝!

一般硬件工程师会采用串联电阻和并联匹配的,或者戴维宁匹配,PCB这块只要保证传输线50偶就行了

要解釋起來還蠻麻煩的 , 但基礎理論卻是很單純 , 就是PCB的電容結構所造成的

另外還有電流的返還路徑問題.

PCB制板时候应该板厂会给具体的阻抗计算值

学习下~~~

留名学习了

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:子类区别

下一篇:请教手工焊接贴片尺寸?