- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

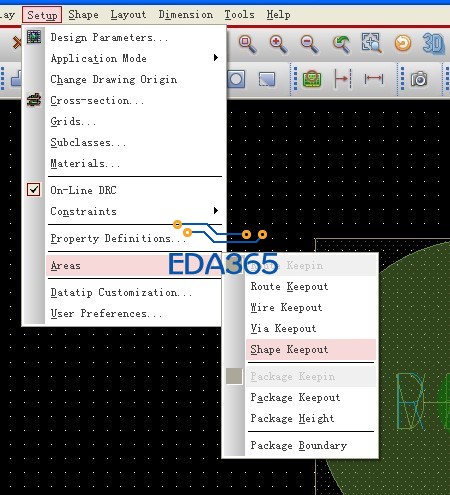

做封装时,把SHAPE KEEPOUR做成圆形

【目的是:在原件的焊盘区域不让铺铜皮,为了好焊接,传热没有那么快,在PCB内DRC时又不让它有错误出现】

如果直接使用shape 把它放在 routekeepout层内,有会出现在PCB内出现错误,

LISTING: 1 element(s)

< DRC ERROR >

Class: DRC ERROR CLASS

Subclass: TOP

Origin xy: (253.68 -62.00)

Constraint: SMD Pin to Route Keepout Spacing

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

Constraint value: 0 MIL

Actual value: 0 MIL

- - - - - - - - - - - - - - - - - - - -

Element type: SHAPE

Class: ROUTE KEEPOUT

Subclass: TOP

- - - - - - - - - - - - - - - - - - - -

Element type: SYMBOL PIN

Class: PIN

PIN: _MARK1.1

pinuse: UNSPEC

location-xy: (234.00 -62.00)

element is on a dummy net

- - - - - - - - - - - - - - - - - - - -

只接点shape add circle 右边options选你要的route keepout层面

会有DRC请到models把pin to route keepout 关掉就好

难得不是用热风焊盘么?

谢大侠们的指点,只是我不想关掉PCB内的DRC,我一直都是在PCB内有个错误,看起来不爽,想把它去掉,又不想直接关掉DRC的错误,不知道那位大侠有新招。

这个元件就MARK点,不知道你们怎么怎么做这个MARK点的。

如果不想關掉 就把route keepout有PAD的地方避開

不過因為Route keepout不能有VOID

所以你必須開一條很小的缺口到route keepout外

其实有drc,在pcb属性里面选择 no drc 就好了,没有必要太纠结。完美的pcb 设计,那是神的事情,而完美却是人。只要确保无电器问题,符合【EMC,safety,SI,PI等】guide和经验以及生产制程要求,基本都不会有什么问题【有仿真的条件的可以先仿真呵呵】

谢指点,因为我刚接触不是很久这个软件,以前都是用PADS的,我以为有大侠可以解决这个问题了。

上楼说,在PCB内不对这个元件做DRC检查,请问一下,是不对这一个元件不做DRC检查,还是不对整个元件不做DRC检查,如果是只对这一个不做DRC检查的话,是怎么处理的?【整个元件不做DRC检查我知道怎么弄】

Allegro规则设置中DRC检查有,ON,OFF,BATCH.请问BATCH是什么意思呀?

选上后会执行什么样的检查了?

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:如下,15.7问题

下一篇:ALLEGRO中丝印位置的一些问题!