- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

设等长遇到问题

录入:edatop.com 点击:

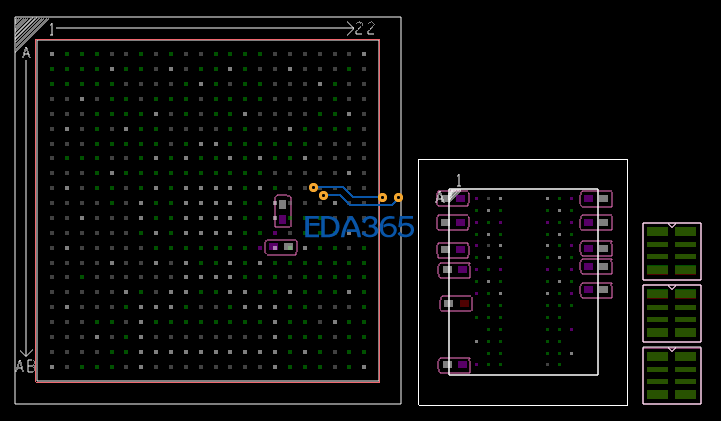

如上图,FPGA、DDR、排阻

DDR在中间

这种情况怎样设等长?

目前设了FPGA到排阻的pin pair等长

但是这样DDR的那段就没有加进去

因为是同一个网络,又无法设置Xnet

请大家指点下,谢谢了

先得确定排阻是干什么用的,目前来看,1.排阻放的位置不对。2.如果排阻放的没问题,那么等长不需要到排阻,直接FPGA到DDR就行

排阻是地址线上拉电阻,等长需要加进去么?

上拉不需要

俺们老大说要加进去

地址是上拉到VTT的吧,第一次听说要加进去……

另外,如果真要加进去,你就得给DDR附模型,

或者直接给PIN强制附模型

对 就是上拉到VTT的

给pin强制附模型 是什么意思?

Edit-Properties,加个pinuse,选bi,就是强制给某个PIN附模型,就可以创建Xnet了

谢谢 按照以上步骤把DDR的pin脚设成BI,但是Xnet还是创建不成功

不知道什么原因

现在的pin pair还是缺少DDR那一段

你排阻附模型了吧,排阻是上拉,不能附。

你可以去让你们老大多看看DDR的设计,这个上拉到VTT是不用算在等长里面的

排阻没有附模型

老大坚持要算进去

即使是错误 的,也要听老大的。不然扣你工资,可能让你以后不爽的。自己知道 就行了。

唉,实在不行你就控制好你的走线方式了,先连到DDR,那样基本没什么误差,你等长控制严格点。

按理那样是应该能加上Xnet的

或者你可以用SigXplorer设置拓扑看看

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:模块复用中元件位号设置的问题

下一篇:SPB16.6的BUG