- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源、地层等,叠层设置里Type栏中一定要选择plane?

差不多吧 负片在运行的时候处理的数据量小一些 但也只是针对上万pin的打板子 才能感觉的 没用过负片还是不要轻易用了 思维方式不习惯 反倒容易出问题

负片确实容易出错,每个焊盘都不能出错,不过也有一定的好处,等你做一块特别复杂的板子的时候,优势就显示出来了,不能全盘否定。其实用一下负片也没什么不好的,如果你永远不碰负片,可能就永远都不会。你的心情我完全理解,自己明明是专业的,却被硬件指来指去,我也遇到过同样的问题,心态放平和,就当自己多学点。

同意楼上。最烦不懂装懂的硬件工程师,;还是在有独立的PCB部门画板比较爽。

plane层可以作为参考层,如果他的等长使用相对延时而非长度做的,叠层的设置对信号的延时有决定作用,也就是叠层设置不对(参考层不对),等长会出问题;shield指的是大面积无分割铜皮,做后仿真可以加快速度,但是,提取拓扑会忽略掉无参考层的区域。

哥们如果做个十层的板子,不说多,就八层吧,如果你快做完了,你需要动一个孔,你会发现,负片的层你根本就不用管他,要是正片,你想想要避让多少层。如果是上万pin的板子,你就是用最牛b的电脑,你看你一天能拉几根线。

硬件工程師要求你這樣做是有道理的.

不要說那個微星10年經驗的 Layout 有多專業 , 恐怕是一點也不專業.

為何要設成 Plane 又定義為 shield , 樓主以為人家是閒閒沒事幹?, 他畫他的電路 , 你做你的 Layout 幹嘛撈過界還比手畫腳. Cadence 又為何在軟體有這些功能設定? 您想過沒有?

不能只由你認為的 Layout 角度來看 , 你要以真正的 Layout 角度來看整個案子. 裡面除了走線布局 , 還有很多 SI 的問題 , 這個 board file 不是只有你在用 , RD 也要用 , 當它們做 SI 分析時不正確的設定 , 問題就出來了.

說實在的 , 我當 Allegro PCB , SI 講師好幾年了 , 論壇上看很多 , 兩岸的 Layout 工程師也看過不少 , 真的能夠稱得上是 Layout 的工程師沒幾個 , 絕大部分僅能算是拉線工.

說這種話不是在標榜自己, 而是感嘆當大家進入這個職場時 , 到底有沒有人真的是負責的把你帶會 , 告訴你為何要這麼做的前因後果... 就算是 Cadence 的 AE 恐怕也沒幾個人有這個能力或經驗也已告訴你吧!

那個何況大家都是口耳相傳 , 四處偷師來充實自己.

好的,谢了。这下明白了。主要无论是之前公司还是现在公司产品都没有特别大板子,以前都是2层为主顶多4层。现在公司的板子最多也就10层,基本都是6层带一片DDR的。那如果我想正规起来,电源地用负片,是不是我库里的所有通孔类焊盘的Thermal relief和Anti Pad都要单独做flash焊盘才能保证不出错?之前刚学的时候我看公司库里的通孔焊盘很少用flash的。大部分是Thermal relief和Anti Pad比前面的Regular Pad大20mil左右,这样不做flash焊盘板子做出来会有问题吗?

谢了,一直想学习SI仿真。自学过。但是网上资料也不多。有时候只能看看人家的模型,发现一些共同点,自己琢磨怎么写模型。后来发现写模型要测IC,一套设备就好贵,民营小公司也不会支持就暂时放弃了。可否拜你为师,自己琢磨总是四处碰壁。

我也算是自學的 .不過我的年紀較大 , 剛進入職場並不是這個行業 , 是當一個業務 , 專門在賣波銲的錫爐然後又轉業當維修工程師 , 是在小型電腦系統與 PCB 生產設備維修上打轉.

因此幾乎看便了整個 PCB 的生產流程及歷史 , 看到我的個人圖片嗎? 那是一台 Digital 的 PDP/11 電腦

這台電腦記憶體只有64KB , 不是DRAM ,而是類似 SRAM 的 Core Memary (磁蕊記憶體 ), 裡面都是雙面板 , 甚至還有繞線板... 這個都是現在一般人看不到的設備.

後來又去維修 Gerber 光學繪圖機 ( 由傳統向量到後來的激光掃瞄 ) .

最後才是到 EDA 這個行業.

當我在看這些軟體操作時 , 就會去回想 PCB 的製程問題 , 慢慢的也演申到 SI / PI領域 .

在這些過程中不乏和原廠 AE 的討論與溝通. 之間令人為之氣結的事不在少數 , 慢慢的忽視到原廠的因素 , 改轉到自我的修行 , 之間的痛苦與無奈大家其實都很類似.

你若想學 SI , 首先最重要的事把基本的物理學 , 尤其是 "波的傳導 " 和基本電學搞清楚. 雖然很多人都在唱高調去研讀大師作品 , 不過就我的看法 , 既然在學校不是學 RF 的本科系要上手 SI , 不要去自找麻煩.

SI 的主要問題不就是阻抗與時序控制而已 , 而這些分析.. 不要看輕自己 , 你以前就學過了, 只是你沒有回想起來 , 沒有聯想到訊號和水波其實是同一種能量的傳導型態. 如果您去學習電磁學 , 裡面也是在這個上面打轉 , 只是用更加精密的數學模型來驗證與推導.

網路上于博士的資料很適合入門者 , 您可以參考.

這是我在別的帖子上的回覆 , 貼過來給您參考

----------------------------------------------------------------

這部分您的觀念有被誤導了.

不是有熱風焊盤才要有Anti-Pad .

其實這是一個備用條件 , 如果您的板子都是正片處理 , 哪根本用不到熱風焊盤 , 更不會有 anti-pad 的需求.

如果裡面有負片電源層 , 這時候要導接的資料會引用您所設定的熱風焊盤圖形來套用 , 若是不同訊號 , 則需要隔開 , 那就要套用 Anti-Pad 來處理.

因為在正片進行導接時 , Allegro 是採用畫一段 Cline 來連接 Pad 和 Sahpe .

可是電源層是禁止走線的 , 那就無法用走線方式來連接 , 這時候系統使採用套上 Falsh symbol 的方式來形成這樣的效果.

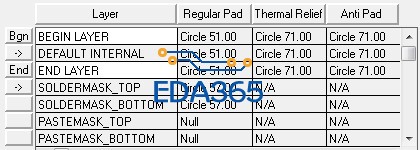

好的。谢啦。看来这下完蛋了。想用负片试试。可是器件库里的孔都是这样做的:假如孔径31mil焊盘51mil的孔。Regular Pad是51mil 的Circle。Thermal Relief和Anti Pad都设置成71mil的Circle。就是焊盘什么形状,Thermal Relief也是什么形状,没有做flash。这样如果应用到负片里我觉得Anti Pad这样设置没问题,反正是起到和不相干的net的铜断开的作用。而Thermal Relief设置成这么一个圆环应该就出问题了吧。这里设置圆环,到负片里这个圆环就是木有铜,导致该连接的却没有连接。我理解的正确吗?

如果要用负片,每个通孔做flash焊盘感觉好麻烦。还是这样设置比焊盘大个20mil木有问题。之前做封装的这么做的,我也就跟着这么做了

如果依照你的 padstack 設計是不適用在負片上 , 如果真的弄成負片 , 保證不能動 .

因為負片電源號全部被隔開了. 您注意到 Anti pad 和 Thermal Relief 呈現在負片上其實是代表把銅給挖掉了.

如果你们公司有CIS、标准库就好了,可以直接使用现成的,不用自己做,或者只做新器件的,flash也可以用现成的

看procomm1722的回复让我学习不少东西啊

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:铜皮上打过孔时,用线条添加画好一个,为了方便,复制,但是不是铜皮的网络?

下一篇:关于Allegro的Toggle的问题