- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

求助原理图问题!

录入:edatop.com 点击:

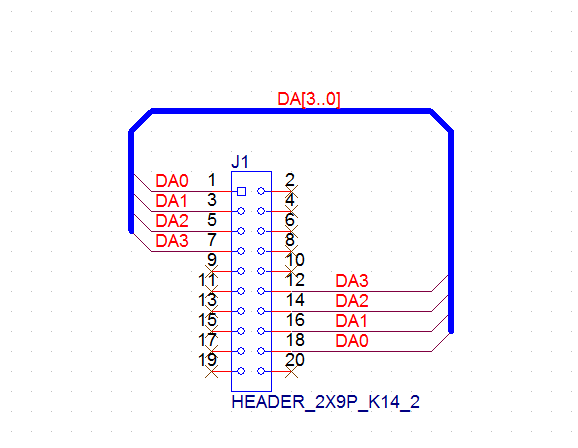

求助:刚学Cadence遇到问题,原理图规则检查时老报错,不知原理图错在哪?请各位大侠相助,不胜感激!

BUS改名为SMD就行了

楼上的不要误导人

BUS和WIRE是不能直连的,要通过BUS entry连接,快捷键e,菜单place里面可以找到,右边的快捷栏也可以找到

按照楼上两位的解决方法,原理图规则检查不报错了,但是生成不了网络表,求解呀......报错如图......

小编,你把不能出网表的LOG文件贴上来啊,要不然怎么知道你错在哪里?

好,如图......

看下你的报错LOG就知道原因了

按照报错LOG改了,还是报错呀

你U3的PCB Footprint填写是不是包含了非法字符?

把pin name改成 NC1 NC2 NC3或者pin的属性定义为power。

哦,不好意思,我没看到LZ没画BUS分支entry,不过我一般BUS名字与分支名字使用一个。

大哥,你开玩笑吧?ORCAD里面BUS和分网络可以用同一个名字?

要不你上个图看看?

LOG都说的这么清楚了

U1 U2 U3 D1 的PCB footprint里面包含非法字符"点(.)",另外还有那么多NC重名,

当然了还有很多错误截图没截到

感谢各位大侠的热心相助,问题已解了;特别感谢chenyuanzhi1989,帮我解决了困扰已久的难题

orcad没听说过总线名与分网络可以不同名,不同名我测试检查是不行的。