- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

layout走线的 阻抗 设计

录入:edatop.com 点击:

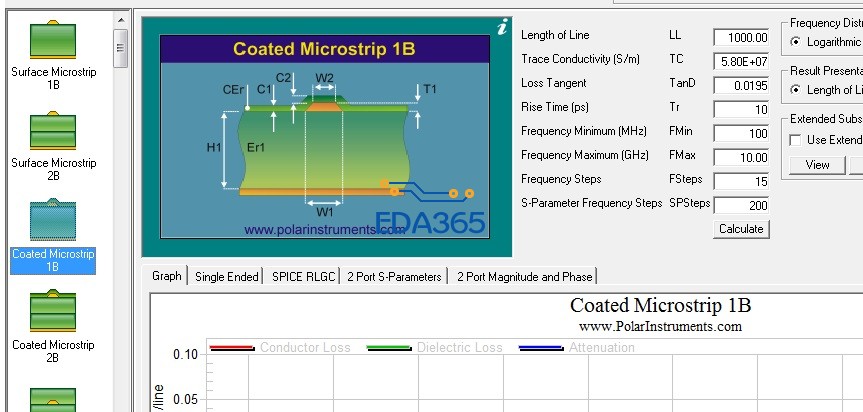

我使用polar si9000进行阻抗计算,使用的是Coated Microshtrip 1B,根据要得到的阻抗来计算线宽,看到里面要求填入的数据如图,不知道这些值一般工艺下都是多少啊,请大神指导。PS 我们的PCB厂家跟我讲线高0.9qz,绝缘材料是PP,不懂什么意思求赐教

我也不懂,进来学习!

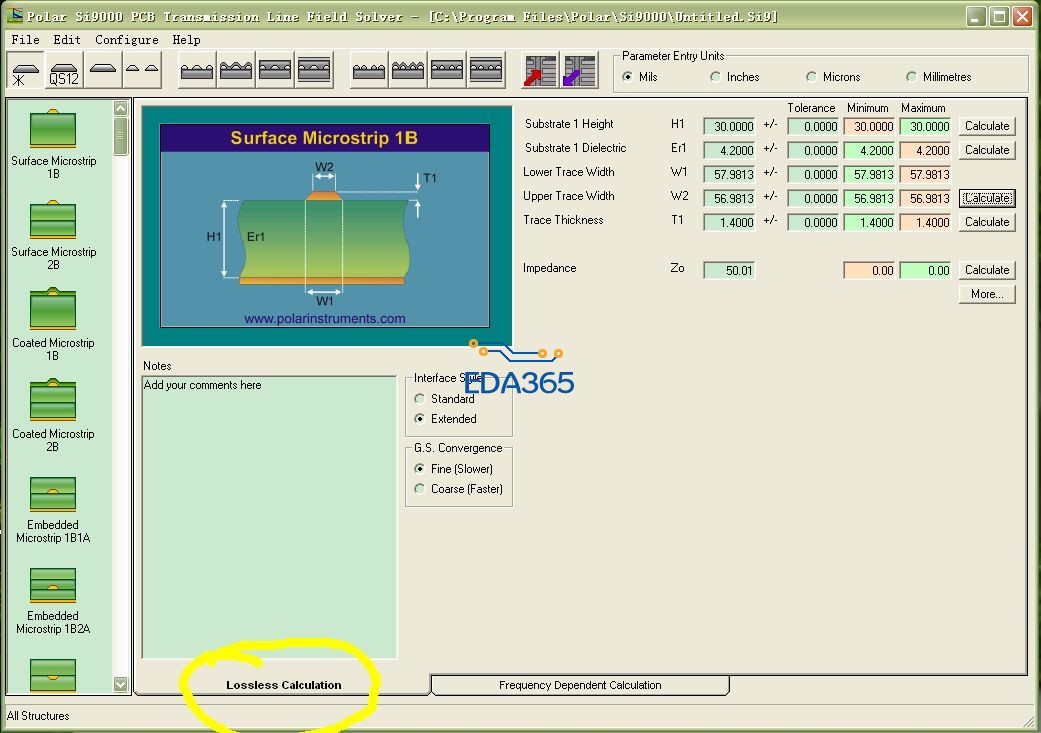

在下方切换一下。换成Lossless Calculation

你看下图:

线宽粗细一点点,对阻抗的影响不是很大的。我算阻抗都是按这些裸铜算的,阻焊厚度没怎么考虑的。

线高就是铜箔厚度,

pp就是铜箔之间的胶,也就是绝缘介质,想一下多层的堆叠结构就知道了。

顺便问下单面板有要算阻抗的吗?

单面板可以用共面模型算阻抗 。和包地是一码事。

如果线的粗细影响不大,板厚的工艺一般变动也不大,那靠什么来得到我想得到的阻抗呢?求赐教

板厚确定,板材确定,介电常数确定,铜厚影响不是很大,阻抗看你要求多少了,一般大多数都是50欧姆,给这些数值相应的输入,阻抗线的线宽就出来了。

你在算出来的线宽基础上+/-几个mil,对阻抗的影响不是很大的。