- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

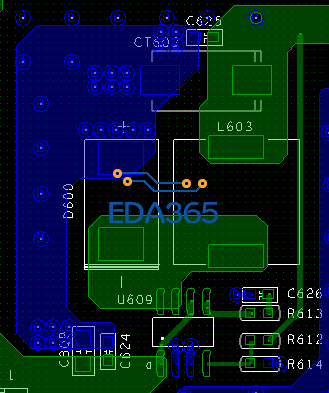

dc-dc布线布局问题

从EMC的角度给点建议,只是我们的一般的开关电源check rule:

1.输入的环路要尽量小:即C609,C624 & U609 & D600的ground pin尽量靠近,尤其C609,C624 & U609

2. 输出的环路要尽量小:即L603 & CT603,C625 &D600的ground pin尽量靠近。

3. L603 &D600 & U609下方共同的那一块shape要尽可能的小,这个是高杂讯区。此区域的相邻层最好为ground shape

你说的纹波问题我不敢肯定是否和layout布局有关,有可能C603选型和选值有关

2楼的回复很到位,这里共享一下当时学习开关电源设计时一些要点,希望对你有所帮助!

开关电源的设计要点

1、电感的取值:电感的取值越大、对纹波的衰减作用越强,但占用PCB 面积较大,不能灵敏的实现输出电压的反馈,动态效果差。

2、开关频率:开关频率越高,则电感和电容的值越小,但开关频率越高 、电源电路的功耗也越大、也不利于EMI的抑制。

3、功耗

4、纹波和噪声:纹波指的是电源波动中的5Mhz以下的低频段,噪声指的 是电源波动中的5Mhz以上的高频段;为了减小这些纹波和噪声可采用加滤波电容和磁珠。

5、上电顺序:可以采用缓启动电路,利用电源芯片的上电速度控制引脚。

开关电源电路的PCB设计注意事项

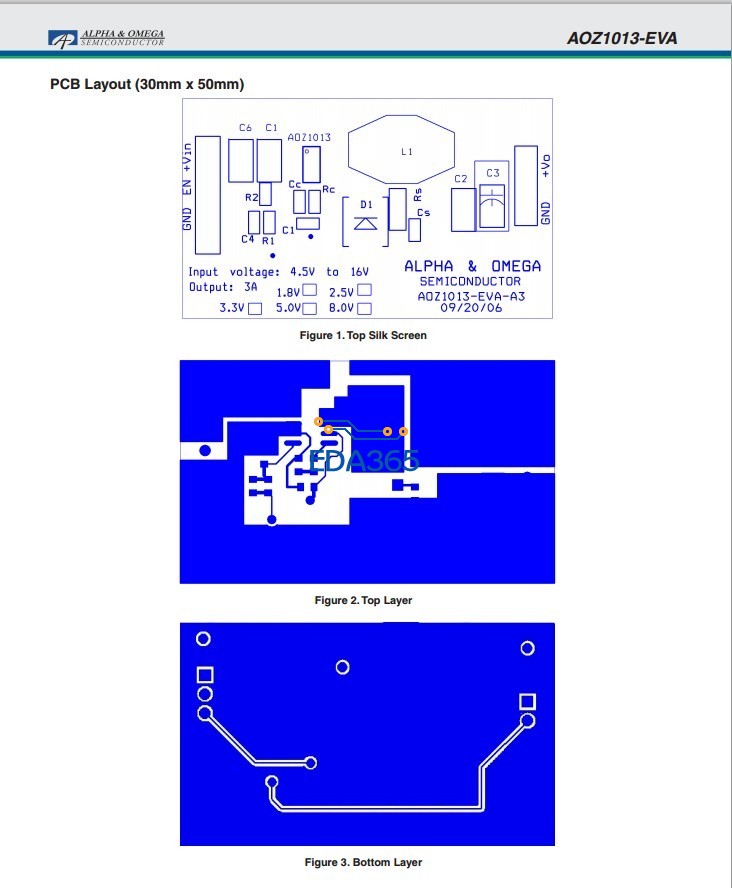

1、最好按照开关电源的数据手册推荐的布局和布线进行设计。

2、输入输出的主通路一定要明晰,留出铺铜和打过孔的位置,注意电容的放置采用大小大小的放置方。

3、开关电源模的布局要紧凑,一字型布局、尽量少打过孔、注意关键滤波器件的放置一定要合理(按照datasheet放)。

4、没有特别要求开关电源及其模内部的信号互联线都需要加粗,一般加粗到10mil(主要考虑sop的焊盘宽度)以上。

5、关键电流通路:需要铺铜处理、注意铺铜的通流能力和打孔的数量。

6、SENSE路径:远离干扰源和大电流的平面上,不要直接将sense线连接在开关电源管脚,一般采用0.5mm的线连到输出滤波电容之后。

7、GATE引脚:尽量粗而短,远离干扰源。

8、INTVCC引脚滤波:这两个电容为快速波动GATE引脚提供电流回路,对电路的正常工作及其重要,一定要就近放置。

9、开关电源及其电感下面最好不要布其他信号线,如果因为空间特别紧张,开关电源放在电感的背面。

10、开关电源的散热焊盘一般需要打散热地过孔。

11、对于输出多路的开关电源尽量使相邻电感之间垂直放置。

12、开关电源的铺铜要特别注意,不要为了追求大电流采用全连接没有隔热路径而使焊接中存在立片、堆锡、虚焊等现象。

13、对于有的原理图将开关电源的地分成PGND、AGND、GND的作大家要查看以下datasheet,一般只有一个GND。

14、输入电源的铺铜面积和过孔数量一定要满足电流要求,有的人一味的追求输出,忽略了输入。

15、开关电源比较高的是电感和大电容,一般不要放置在焊接面,注意高度限制。

16、切记遇到开关电源的第一任务是下载datasheet,看一下开关电源的结构、电流大小、sense管脚、推荐电路等,不要想当然!

17、开关电源地孔的个数要与电源过孔的个数相当。

1,布局的地不是很好,电容,二极管和IC的功率地尽可能的小,靠近。然后单点接。

2,你的FB走线决定了你的纹波不可能在50mv以下,FB最大的忌讳就是从DCDC的电感下面或者旁边走。

我实际验证过,同样的布局,FB走电感下面纹波150mv以上,距电感3mm左右,中间加地隔离,100mil一个过孔,纹波80左右,如果FB走背面(4层板),纹波30左右。同时这个值和设计有关,我验证的是5-3.3V的DCDC,FB=0.6V,3.3/0.6=5.5倍左右和你的DC5/0.8=5相当,耦合到FB走线上的噪声会放大5倍。

所以个人觉得最大问题应该是FB走线,建议修改,DCDC的FB要当作非常紧要的模拟量来处理,不然电源质量得不到保证。

小编可以看看这个帖子,我用的AOZ1050芯片。

http://www.eda365.com/thread-88478-1-1.html

刚开始的时候也遇到纹波很大的问题。并且12V转1.2V的时候频率都不能稳定下来。

从图上看,我觉得布局没有太大的问题。

可以从这几个方面着手:

1、看看纹波的频率是否稳定在400~500K的某个频率上?

2、L603的电感量是否饱和,因为功率电感有个±20%的误差参数,建议电感量取的稍微大一点。

3、输出电容采用大容量的钽电容能够比较明显改善纹波。

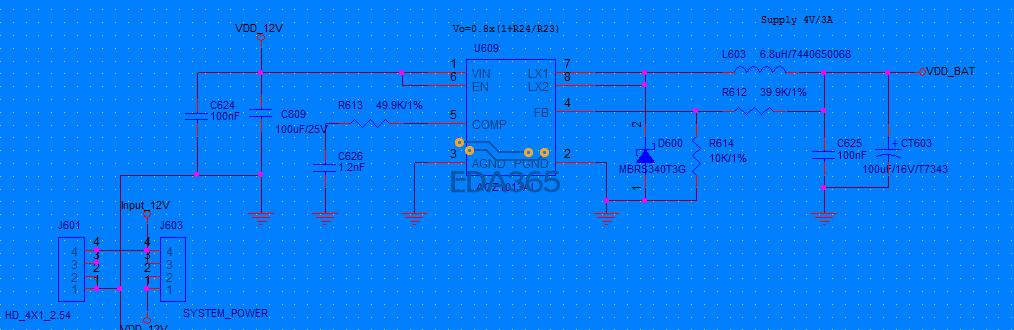

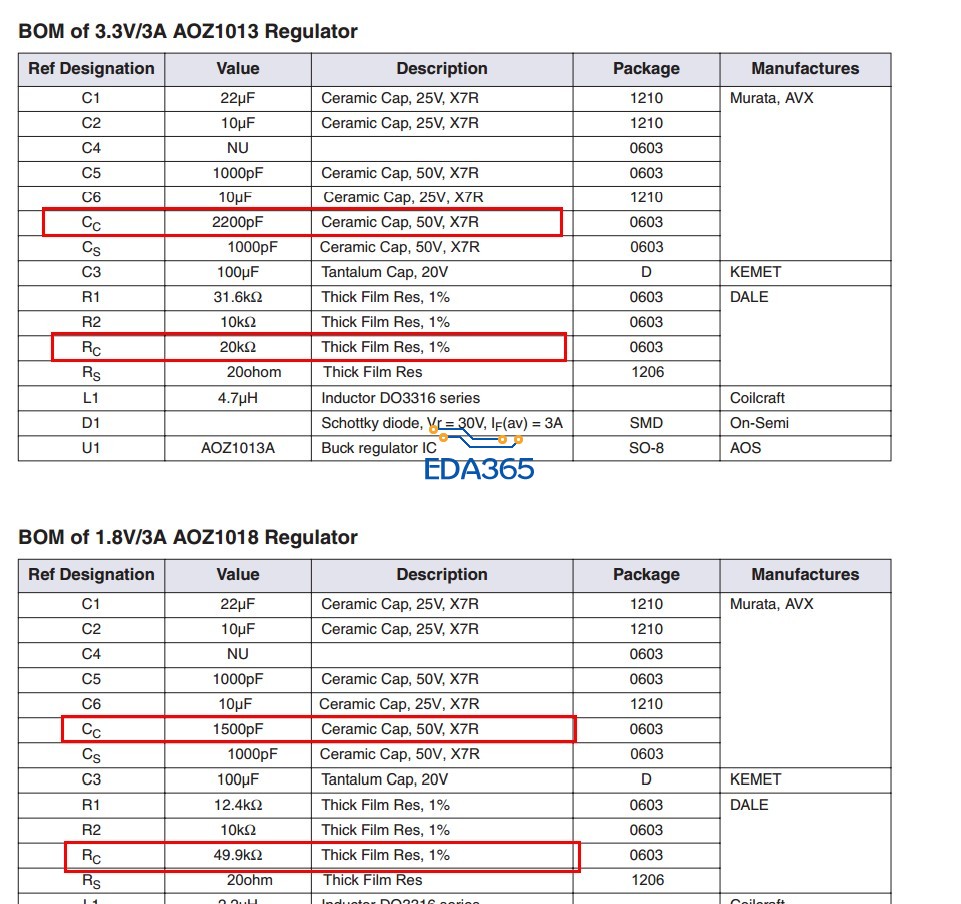

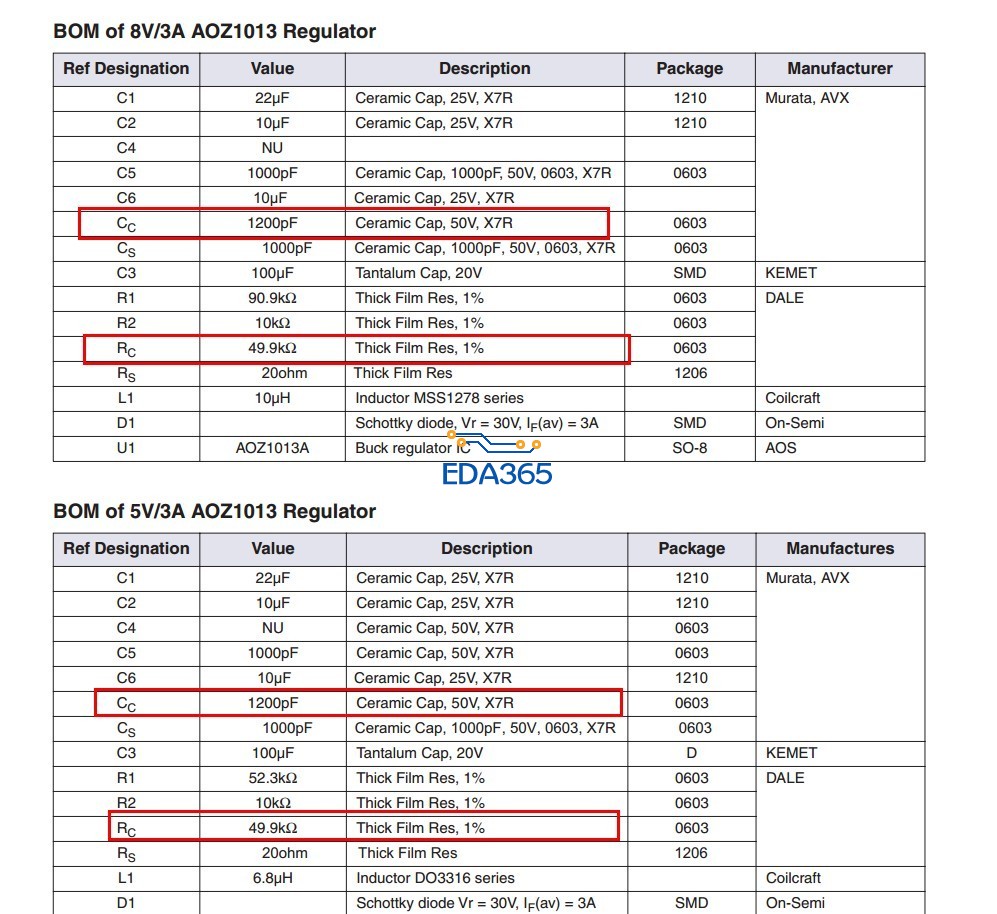

4、注意AOZ1013的5号引脚,调整合适的环路补偿参数。

我的实际调试经验是通过示波器观察AOZ1050的工作频率,发现没有稳定在431KHz上,然后通过增大输出电感,输出并联220uF钽电容,改变都不明显,将环路补偿参数调整后纹波成功下降到了15mVp-p左右。

附件为官方网站提供的参数计算工具(将.rar扩展名改为.xls),一点愚见,希望对你有帮助。EZBuck_ver2_1.rar(1003.5 KB, 下载次数: 55)

2013-7-14 22:11 上传

点击文件名下载附件将rar扩展名改为.xls

另外4楼说的很对,FB走线的确离电感近了。

小编可以看看官方的参考设计:AOZ1013AI-EVA.pdf(828.11 KB, 下载次数: 57)

2013-7-14 22:28 上传

点击文件名下载附件

长见识了 谢谢各位

楼上的都解释的很好。你的输入输出GND,也不要连在一起,还有就是人家说的FB了

楼上各位说的都挺给力的,我也从走线上提点建议,1、L电感两pin之间的空间不要走铜皮,电感的寄生串联电容量应该尽量减少,所以电感引脚之间的距离越远越好,所以你 L603 &D600 & U609共同的那一块shape修一下,2、看你布局拉得挺开的,想c624这样的小电容可以靠近一点输入管脚,3、en使能可以断开走背面,把输入的地和芯片的地pin连接4、馈线走bot层或者换内层,同样避开电感

另外真正属于FB部分的应该是R612 R614到芯片pin脚这部分,这部分应该走粗,而不是你r612到采样点的走线走很粗,一般都走一样的线宽15 20mil 基本没问题

果然有专业人士在啊!我也沾光学习点。呵呵!

Mark一下

非常感谢大家的帮助,太感谢了!

大家有没有对输出电容容值的定量计算公式呢?到底用多大容值的为好!datasheet上说,越大越好,我想它应该跟L,I &ripple 有关系的 来降低纹波

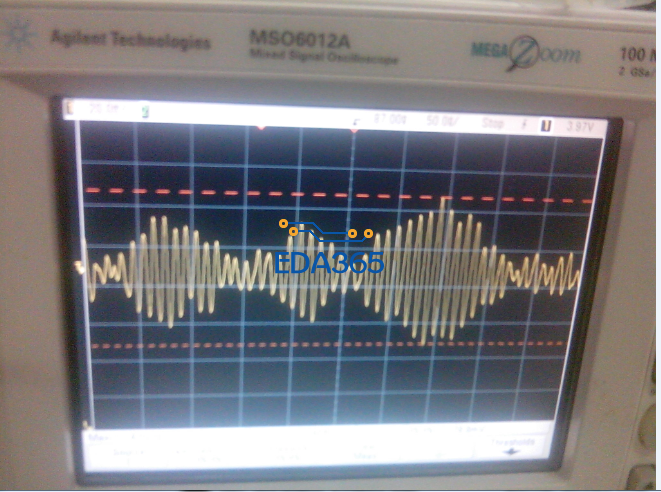

你好,非常感谢你的帮助,分享你的经验。你说的工作频率是芯片7 8 两引脚上的开关频率吗?我用示波器测得是这样的波形,不知道是不是正常的,能帮我分析一下吗? 第一张 图是测得的 7 脚的波形,第二张图是测得的输出的电压 (20mv/div)的波形,pk-pk 大的话有100mv

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:为什么设esc为cancel的快捷键没能生效?

下一篇:新手allegro问题请教