- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro DRC 问题

录入:edatop.com 点击:

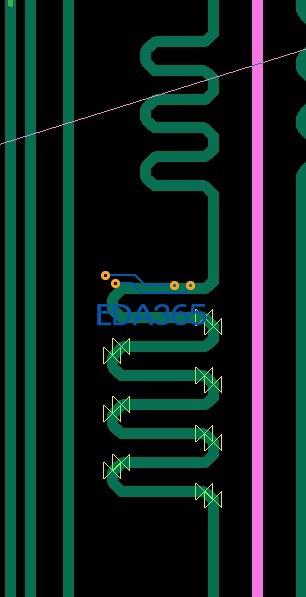

今天在绕DDR Data等长时,发现为什么有时候显示DRC,有时候不显示DRC,也Update DRC和DB doctor都没有作用,求解?

约束区设置线距:18.5

图片所示:

上面一节为10的线距

下面一节为18.5的线距.

为什么上面不报错,下面的会报错,求解!

可能上面的有画constraints,你打开看看

上面是不是有区域规则?

很有可能是下面有区域规则

看看报的是什么DRC,对症下药;

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:placebound top 层 和 assembly top层是否可以在PCB上显示出来?

下一篇:原理图建库的问题