- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

关于XNET极其怪异的问题求救各位大侠

录入:edatop.com 点击:

各位大侠,小弟最近在学用Allegro画一块扩展板,原理图用的是Concept HDL,板子的情况是通过一个160pin的连接器将主板上的flash接口信号输入到扩展板上的flash芯片,总共两个通道(两组flash接口信号),每个通道接4个flash芯片,在连接器和芯片之间串了33ohm的电阻排。现在的问题是都是相同的设计,结果出现了两种结果。

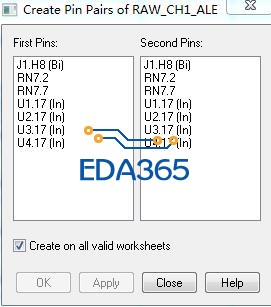

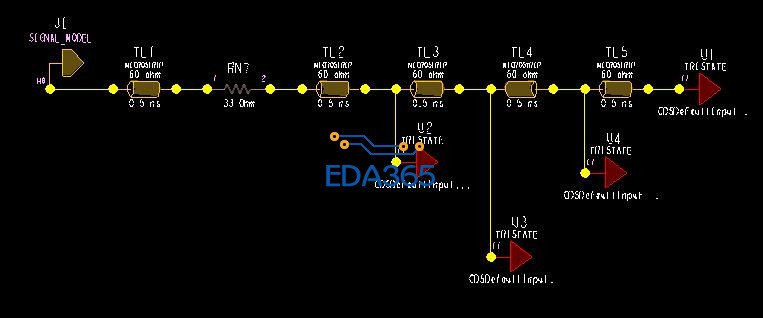

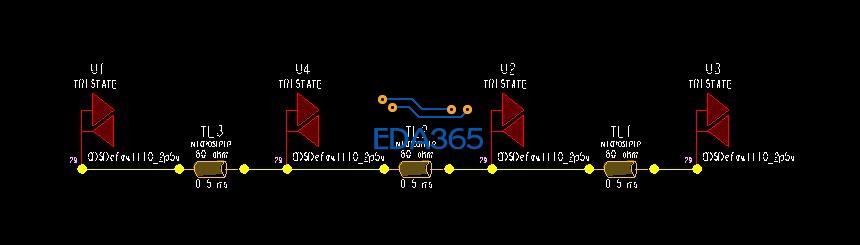

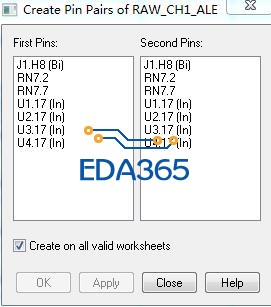

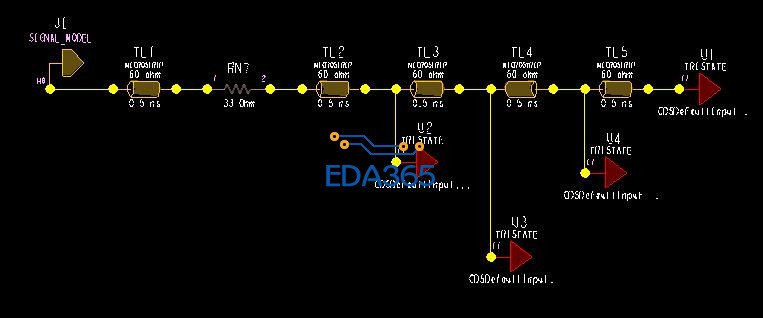

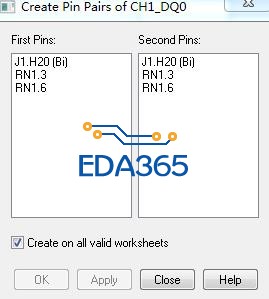

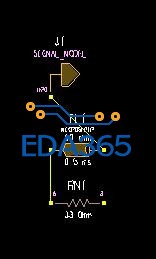

对于连接到芯片的输入或输出管脚的控制信号,软件能把连接器的相应管脚到芯片管脚的相应电路都放在一个XNET里边,做Pin Pair时能和设计意图一致,没有任何问题,拓扑图和Pin Pair选项截图如下。

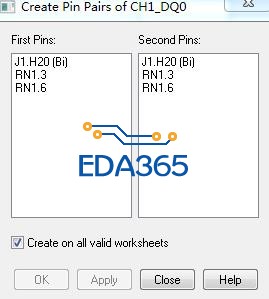

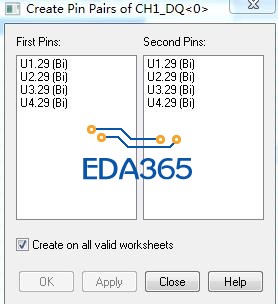

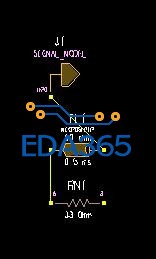

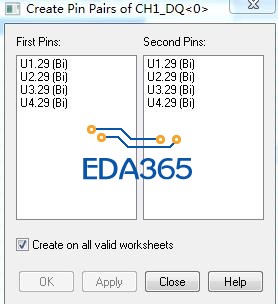

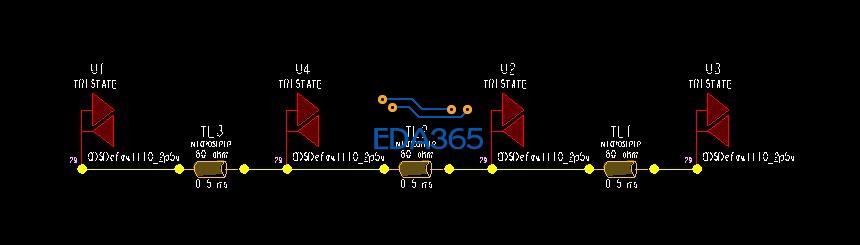

但是对于连接到芯片的双向的数据信号,软件竟然把整个通路截成了两段,从连接器到电阻排是一个XNET,而电阻排以后的4个芯片相连的管脚自己组成了一个net,拓扑图是断开的,而且Pin Pair也不能做到一起,如下图。

在此先谢谢各位大侠了

对于连接到芯片的输入或输出管脚的控制信号,软件能把连接器的相应管脚到芯片管脚的相应电路都放在一个XNET里边,做Pin Pair时能和设计意图一致,没有任何问题,拓扑图和Pin Pair选项截图如下。

但是对于连接到芯片的双向的数据信号,软件竟然把整个通路截成了两段,从连接器到电阻排是一个XNET,而电阻排以后的4个芯片相连的管脚自己组成了一个net,拓扑图是断开的,而且Pin Pair也不能做到一起,如下图。

在此先谢谢各位大侠了

通常會有這種現象是 SI 的環境設置不完整所導致.

其中最重要的是 DC Net , 很多人都忽略 DC Net 的設定對整體的影響 , 只注意被動元件的 Model 而已就有機會發生這種現象.

谢谢您的回复,相应的DC net已经设置完了,但是没有变化。关于上面的异常,还有非常奇怪的一点是我的电阻排的一个引脚是和芯片的数据脚连接的,但是在Pin Pair和拓扑图里这个电阻排的引脚都没出现,这个太怪异了

查到问题了,谢谢各位大侠关注

xnet不完整时候,需要仔细确认每个电阻的模型是否都已经创建了,有时需要手动创建r/c模型

谢谢您的回复。不过不是这个问题,而是我犯了一个低级错误,自己都不好意思说了,呵呵

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:导入网标报错

下一篇:allegro中如何对齐元器件