- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

设置相对等长

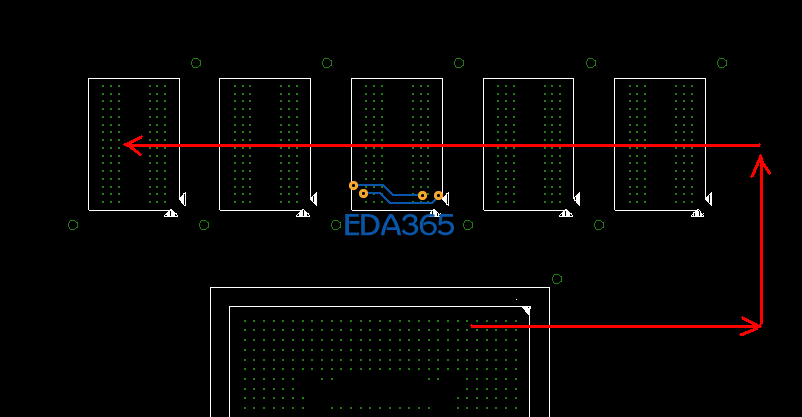

CPU带5片DDR3,ADDR那边设置相对等长处理处理。见下图:

不用sigxplorer这样来建规则,这样设置的如果拓扑结构不一样,比如多个下拉电阻,还有时钟跟ADDR的拓扑肯定不一样,很麻烦。

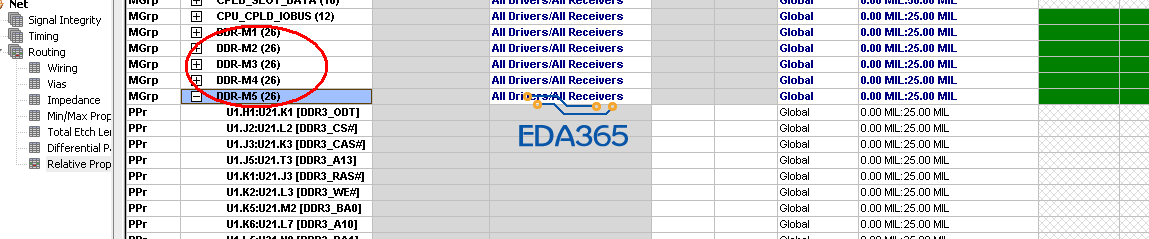

有没有更好的方法要设置规则,如下图:

今天研究这个规则 ,搞了好久,都没设置成功,望高手指点一下,先一谢过了。

我自己的做法是主芯片到第一颗等长

然后依次相邻DDR间走线等长

另外dqs 和data单独组内等长就是了

sigxplorer的设置是最严格明确的设置;cm上设置只是简单初级的做法,只适合点对点拓扑。

match group本质就是约束管脚对。你自己想下,在多点拓扑结构中,如果你不指定要约束哪对管脚对,那软件怎么知道你要约束哪对管脚对?

所以,sigxplorer的作用就是让你指定好管脚对,再对它们进行约束。

至于你说拓扑结构不一样,要分别设置很麻烦;这是必然的,拓扑结构都不一样,软件怎么给你类比过去设置呢?

现在先把约束分为四组:时钟,命令,控制,数据,然后组内根据拓扑不同,再进行细分设置。

不是有IPC作品吗。参考就是了。

将一组地址线建立match group后,只能对里面的一个net来用sigxplorer,后面其他的都用这种规则。

这样在All Constraints/User Define下面,可以看到你用sigxplorer建的那个ECS。

但是我这边的这个板子,地址,时钟,控制线用的是同一种规则,而且也没有ECS.

这是如何建立的?

说明你不是很会用sigxplorer啊,找点资料看下呗

不知道是sigxplorer的Bug还是软件使用不精,多节点的net用sigxplorer生成的match group模版复用到其他net时,会出现同一个match group里面有不同芯片的管脚,而且互相乱跳,不知道大家碰到过没有。后来,自己写个skill,根据bus里面的网络自动创建pinpair,把同一个芯片的pinpair创建成match group,一了百了。

朋友 ,这个SKILL能分享下不!

是遇到乱跳情况,原来是bug

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:原理图技巧求学,求指教!

下一篇:只显示部分元件位号