- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Allegro網表導入問題

录入:edatop.com 点击:

將網標導入Allegro時,由於有些封裝比原理圖中多一些引腳,如螺絲孔、IC的散熱PAD,而導致報錯,這個問題怎麼辦啊?

原理图库必须与pcb封装匹配,在原理图库里把没有的引脚加上

散熱PAD 就回 DSN裡面去增加引腳

螺絲孔,定位孔,這個沒有影響吧

重新建封装,然后重导网标,放置器件

删掉PCB封装引脚编号,

那請問如果我在PCB圖中要增加原理圖中不存在的元件和電氣連接,改怎麼做呢,麻煩了》

在logic-part logic下面就可以添加元件,给添加的元件附上net是中logic-net logic下面,自己试一下就知道了。

但建议最好不要这样做,这样不利于之后的检查,最好还是在原理图里修改,再重导网表。

如果有电气属性的元件还是在原理图里面改比较好。如果是一些结构件,可以直接place mechanical symbols

这些都是没有电气属性的,放在pad时,选择mechanical 就OK了

這個是有屬性的,比如要放一些接地的Dummy pad.

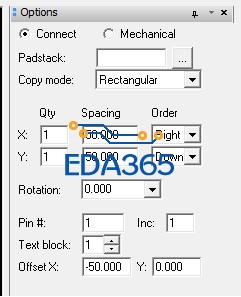

不好意思,我再問個問題,我創建的封裝的Pin number總是很大,線條也不夠粗,而且也不在Pin的中心,請問這個怎麼調節呢?

放置PIN的時候 在OPTION裡面可以調

基本設定是偏左 OFFSET 你可以注意一下

Cadence Allegro 培训套装,视频教学,直观易学

上一篇:15.5安装了移动不了?

下一篇:SPB 16.6 問題請教