- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

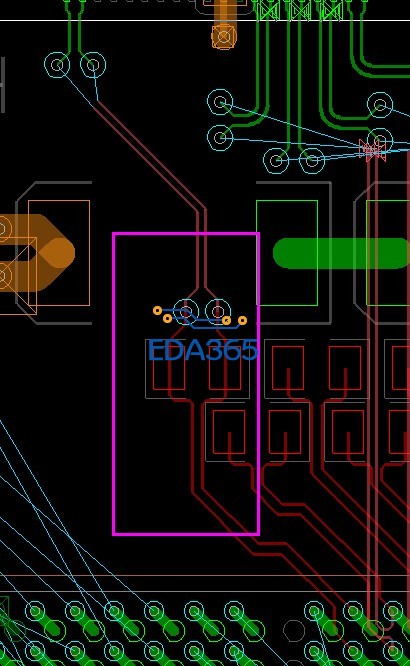

求教并联终端匹配电阻PCB布局布线大家是怎么放置的?

1

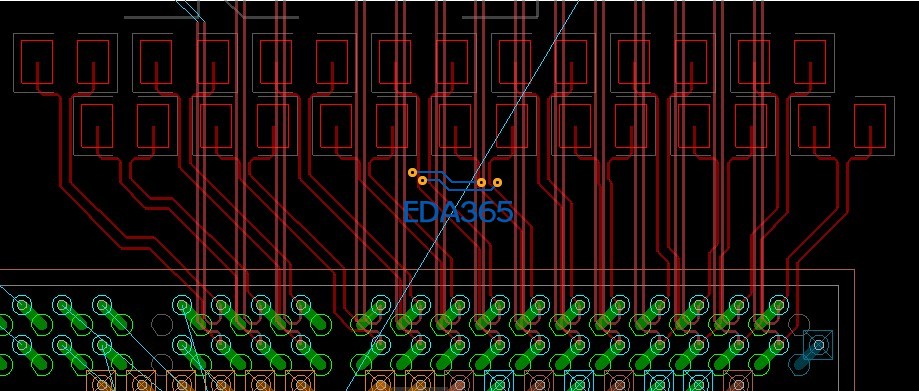

两种图的区别:前者匹配位于接收端之前,后者位于接收端之后

1,当匹配电阻位于接收端前面时候,如果匹配电阻距离接收器很远,将有一段可被视为传输线的PCB 连线得不到应有的阻抗匹配,从而导致信号在接收端产生反射现象,这样就会大大降低了接收端信号的质量。所以如果使用这种方式,应保证这一部分走线足够短(实际测量对于一般LVTTL电平大约100mil的距离会使得信号过冲增大几十mv).当实际的PCB布局中,这种处理很难保证电阻到接收端的距离。

2,当电阻位于接收端之后时,接收端的波形非常接近匹配电阻位于理想位置的波形,只是波形的延迟更大,这个延迟近似等于这个电阻与接收器之间的传输线的延迟,对于一般情况,这一段线应该在10mm之内,延迟大约在70ps以内,对于1G左右的信号,是完全可以忽略的,而且这种布局在PCB的处理上更容易实现,所以此中方式更常用,且不易出问题。

看帖子要沉了 自己先顶一下

没看出个所以然,你说的图1是下面的图,但是与上面的是一样的布局,这样放置可以,只是两排电阻太近,靠下面的一排过孔没位置扇出,不过就像你说的,把握好靠近主芯片的原则就好!

嗯 你分析的很有道理,我知道第二种更适合,也能明白电阻的阻值一般跟阻抗线的阻抗值大小一致,且越靠近后端pin脚越近越好,另外我想问一下这个10MM的后端拉线是经验值吗?怎么感觉这么大,400mil啊!还有那超过1G的速率的会造成什么样的不良影响,也有参考经验值?

谢谢你的回答,但是你没看懂这个问题,一张图是从BGA接线经过匹配电阻串联接到AD,一张图是从BGA直接拉线到AD,BGA后端并联接一个匹配电阻。

一般来说这几匹配一般都是BGA,按个人经验10mm在这种情况是比较大的了,而且前面计算过程还是留了很大余量的。除非引脚在大的BGA中间,但芯片设计的人一般不会这么2。但大家都懂得即使用第二种也要尽量靠近最优嘛毕竟,时序余量还是不要太极限了。

太长的话影响还是时序方面的,但看你查分类型了,如果像USB这种就一对,就不存在,只要差分间误差保证,这个电阻放个1000mil远也不存在,因为延时对2根线都延时了,但很显然,线分支越长,受干扰的几率就越大。 如果是并行的接口,那显然,各个查分对之间时序也是有要求的,那么各个差分这一段的长度也应该等长来保证时序冗余,不过目前我还没遇到过这一截线有什么差距的情况,基本都差不多,相差一般都在一两百mil之内。

明白了 谢谢你的耐心指导

顶2楼的原理分析,一般推荐匹配电阻放置在接受端的后方。